# APPLYING MODEL CHECKING TO ANALYSING SAFETY INSTRUMENTED SYSTEMS

Matti Koskimies

TEKNILLINEN KORKEAKOULU TEKNISKA HÖGSKOLAN HELSINKI UNIVERSITY OF TECHNOLOGY TECHNISCHE UNIVERSITÄT HELSINKI UNIVERSITE DE TECHNOLOGIE D'HELSINKI

# APPLYING MODEL CHECKING TO ANALYSING SAFETY INSTRUMENTED SYSTEMS

Matti Koskimies

Helsinki University of Technology Faculty of Information and Natural Sciences Department of Information and Computer Science

Teknillinen korkeakoulu Informaatio- ja luonnontieteiden tiedekunta Tietojenkäsittelytieteen laitos Distribution: Helsinki University of Technology Faculty of Information and Natural Sciences Department of Information and Computer Science P.O.Box 5400 FI-02015 TKK FINLAND URL: http://ics.tkk.fi Tel. +358 9 451 1 Fax +358 9 451 3369 E-mail: series@ics.tkk.fi

© Matti Koskimies

ISBN 978-951-22-9477-0 (Print) ISBN 978-951-22-9478-7 (Online) ISSN 1797-5034 (Print) ISSN 1797-5042 (Online) URL: http://www.otalib.fi/tkk/edoc/

TKK ICS Espoo 2008 **ABSTRACT:** There is an ongoing change in the industry in which old analogue instrumentation and control (I&C) systems are replaced with new digital ones. New digital systems enable more complex control tasks and especially their application to safety instrumented systems (SIS) has created a need for new verification methods such as model checking.

Our goal is to study the applicability of model checking methods to a real safety instrumented system used in industry and to evaluate whether such a system can be modelled on a level which, on one hand, enables verification of relevant safety properties and, on the other hand, keeps the size of the model feasible. A central objective is also to create a general methodology for applying model checking to analysing safety instrumented systems.

As a case study we modelled an application of UTU Falcon arc protection system along with it's environment with NuSMV modelling language. Moreover, we used NuSMV to verify this model against the most relevant safety properties for the system.

Our results indicate that model checking seems to be a promising method for verification of safety instrumented systems.

**KEYWORDS:** Model checking, safety instrumented systems

# CONTENTS

| List of Figures vi<br>List of Tables vii |                                                                                                                                                                                                                                                                                                                                                                 |                                                  |  |  |                          |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--|--|--------------------------|

|                                          |                                                                                                                                                                                                                                                                                                                                                                 |                                                  |  |  | List of Abbreviations ix |

| 1                                        | Introduction         1.1       Outline of the Report                                                                                                                                                                                                                                                                                                            | 1<br>2                                           |  |  |                          |

| 2                                        | Models and Analysis of Control Systems2.1Formal Methods for Digital Automation Systems2.2Overview on PLCs2.3Classification Criteria for PLC Models2.4Survey of Studies on Model Checking PLCs2.4.1Previous Surveys2.4.2Modelling PLC Applications2.4.3Methods for Synthesising PLC Programs from Models2.5Overall Status of the Research on Model Checking PLCs | <b>3</b><br>3<br>4<br>5<br>6<br>6<br>6<br>8<br>9 |  |  |                          |

| 3                                        | Safety Instrumented Systems3.1Overview on Safety Instrumented Systems3.2An Abstract Model of Safety Instrumented Systems3.3Classification of the Abstract SIS Model                                                                                                                                                                                             | 10<br>10<br>10<br>13                             |  |  |                          |

| 4                                        | Modelling and Analysing Systems with NuSMV4.1General Overview4.2Modelling with NuSMV4.2.1General Structure of NuSMV Models4.2.2Structure of a Module Declaration4.2.3Semantics of NuSMV Models4.3Specifying Properties with NuSMV4.3.1Semantics of PLTL formulas                                                                                                | 14<br>14<br>14<br>14<br>14<br>17<br>18<br>19     |  |  |                          |

| 5                                        | Modelling Safety Instrumented Systems with NuSMV         5.1       Modelling the Controller                                                                                                                                                                                                                                                                     | <b>21</b><br>21<br>22<br>23<br>25<br>27          |  |  |                          |

| 6                                        | Case Study: Electric Arc Protection System         6.1       Overview of the Falcon System                                                                                                                                                                                                                                                                      | 28<br>28<br>30<br>30<br>30<br>30<br>32<br>32     |  |  |                          |

|                 | 6.3.1 Verified Properties                         |                                        | 33              |  |  |

|-----------------|---------------------------------------------------|----------------------------------------|-----------------|--|--|

|                 | 6.3.2 Information Required for Verification       |                                        | 33              |  |  |

|                 | 6.3.3 Description of the Application              |                                        | 35              |  |  |

|                 | 6.3.4 Assumptions of the System                   |                                        |                 |  |  |

|                 | 6.3.5 Description of the NuSMV Model              |                                        | 39              |  |  |

|                 | 6.3.6                                             | Specification of Properties with NuSMV | 46              |  |  |

|                 | 6.3.7                                             | Experimental Results                   | 47              |  |  |

| 7               | <b>Conclusions</b><br>7.1 Future Work             |                                        | <b>49</b><br>50 |  |  |

| Bibliography 51 |                                                   |                                        |                 |  |  |

| A               | Full Source Code of the NuSMV Model — Case 1      |                                        |                 |  |  |

| B               | Full Source Code of the NuSMV Model - Case 2    5 |                                        |                 |  |  |

## LIST OF FIGURES

| 1                                                                       | An abstract model of a SIS                                      | 11 |

|-------------------------------------------------------------------------|-----------------------------------------------------------------|----|

| 2                                                                       | An example of a NuSMV model                                     | 15 |

| 3                                                                       | State diagram of the running example                            | 18 |

| 4                                                                       | Input/output behaviour of the Delay module                      | 21 |

| 5                                                                       | Implementation of the Delay module                              | 22 |

| 6                                                                       | An outline for the implementation of the Controller module .    | 23 |

| 7 Implementation of Logic <sub>e</sub> and Memory parts of the abstract |                                                                 |    |

|                                                                         | SIS model                                                       | 24 |

| 8                                                                       | Implementation of the Inputs of the abstract SIS model          | 25 |

| 9                                                                       | Input/output behaviour of the Timer module                      | 26 |

| 10                                                                      | Implementation of the Timer module                              | 26 |

| 11                                                                      | Implementation of the OneShotTimer module                       | 27 |

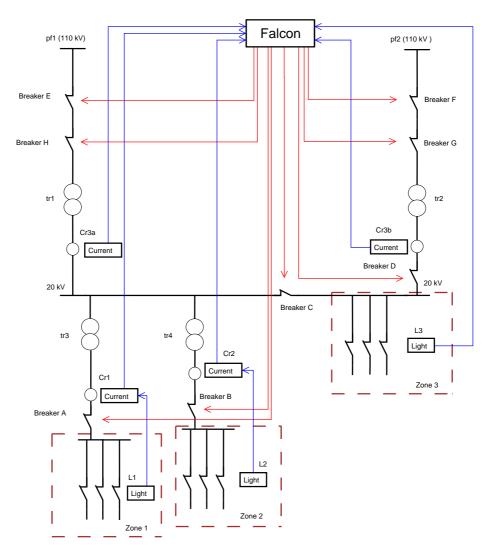

| 12                                                                      | The Falcon Protection System                                    | 28 |

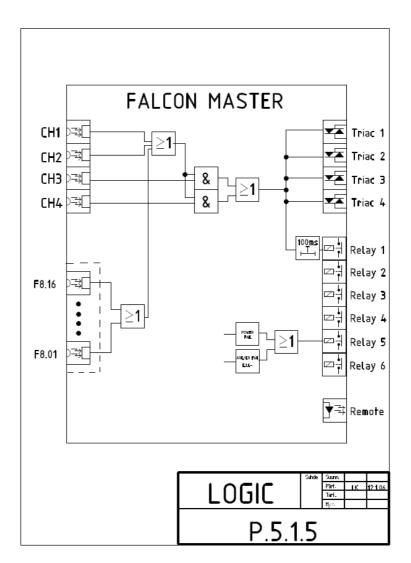

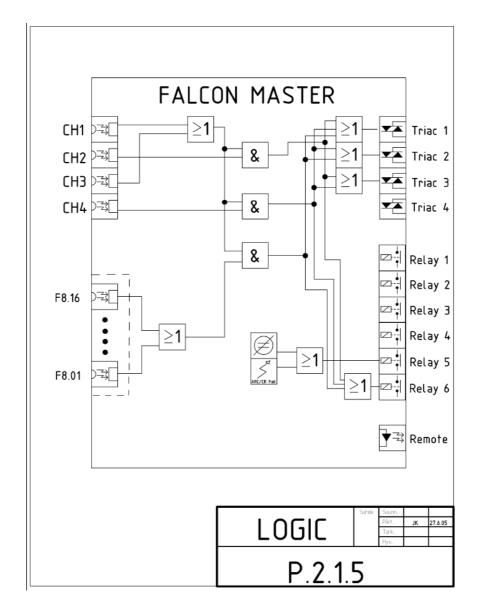

| 13                                                                      | A tripping logic of the Falcon system                           | 29 |

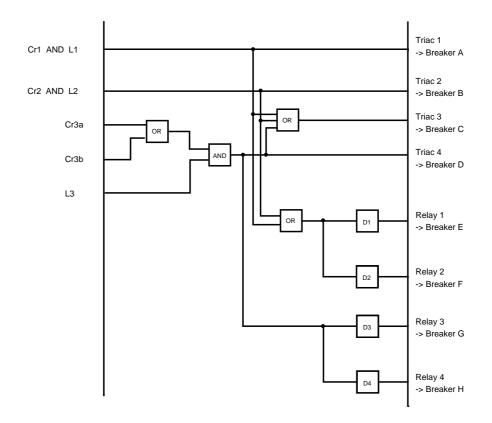

| 14                                                                      | Tripping logic diagram of the example system                    | 31 |

| 15                                                                      | Truth table representation of the specification of the tripping |    |

|                                                                         | logic of the example system                                     | 32 |

| 16                                                                      | Switch diagram of the example system                            | 36 |

| 17                                                                      | Tripping logic of the example system                            | 37 |

| 18                                                                      | Data flow between NuSMV modules                                 | 39 |

| 19                                                                      | Controller module                                               | 41 |

| 20                                                                      | Breaker module                                                  | 44 |

| 21                                                                      | UTU_ARC module                                                  | 44 |

| 22                                                                      | UTU_CR module                                                   |    |

| 23                                                                      | Implementation of the Current flow model                        | 45 |

## LIST OF TABLES

| Actions caused by alarms on different protection zones     | 37                                                                             |

|------------------------------------------------------------|--------------------------------------------------------------------------------|

| Running times of the model checking process with different |                                                                                |

| parameter values                                           | 48                                                                             |

| Running times of the model checking process with insuffi-  |                                                                                |

| cient parameter values                                     | 48                                                                             |

|                                                            | Running times of the model checking process with different<br>parameter values |

## LIST OF ABBREVIATIONS

DCS Distributed Control System

FBD Function Block Diagram

I&C Instrumentation and Control

IL Instruction List

LD Ladder Diagram

NPP Nuclear Power Plant

(O)BDD (Ordered) Binary Decision Diagram

PLC Programmable Logic Controller

SAT Propositional Satisfiability

SFC Sequential Function Chart

SMV Simple Model Verifier

ST Structured Text

## **1** INTRODUCTION

Instrumentation and control (I&C) systems are an important part in the operation of nuclear power plants and many other industrial facilities. They are divided into basic process control systems (BPCS) and safety instrumented systems (SIS). The basic process control systems are related to the main functions of plants, e.g., to tasks related to energy production [14]. The safety instrumented systems are used to implement safety related functions such as emergency shutdown systems [14]. The nuclear power plants that are currently in active use in Finland have been built at the time when I&C systems were implemented by using analogue hardwired circuits and electromechanical relays. In many other countries the situation is the same. As these power plants are starting to be at the end of their life cycle, there is an ongoing process in which the plants are being renewed and modernised in order to extend their lifetime. An important part of this renewal is the replacement of the old analogue instrumentation and control (I&C) systems by new digitalised ones.

Traditionally, the verification of I&C systems (both analogue and digital ones) has been based on manual testing or simulation [32]. In manual testing an actual system is tested against human- or machine-generated test cases. In simulation a system is tested by simulating the behaviour of a model of the system with a simulator. However, as the implementation of I&C systems with digital programmable logic controllers (PLC) has enabled more and more complex control logic designs the traditional verification methods are becoming insufficient [32]. Especially, as new digital PLC based systems are used to replace old analogue safety instrumented system in highly safety critical domains such as nuclear power plants, new verification methods are needed.

Alternatives for new verification methods for I&C systems include formal verification methods [13]. Formal verification refers to the act of proving or disproving mathematically the correctness of design of a system. The benefit of this approach is that formal methods are at best fully automated and exhaustive, i.e., they analyse a given system with respect to its all possible behaviours. A promising formal method for the verification of I&C systems is model checking [9]. In model checking, the basic idea is to verify whether a model of a system fulfils the specification of the system. This is done by analysing all possible behaviours of the model. In practice, model checking is carried out by first modelling a given system by the input language of a model checker. Next the properties that the system is supposed to fulfil are specified by using a suitable specification language such as temporal logic. Finally, a model checker is used to verify that the model of the system fulfils the specified properties. The key difference compared to simulation method is that the verification is done against all possible executions of the system. Moreover, if a specified property is violated, model checker returns a counterexample of the violation, i.e., an execution of the model that violates the property. One of the key challenges for the model checking method is so-called state explosion problem [9] which, informally speaking, refers to the exponential growth of number of possible states of a system to the size of the system description. Thus, currently model checking is not a feasible verification method for arbitrary sized systems.

There has already been a notable number of studies on applying model checking to PLC based I&C systems [18] and this work is a continuation to that research area. Our goal is to study the applicability of model checking to safety instrumented systems by considering a real world case study. Moreover, we introduce a general methodology for applying model checking to similar systems as the case study that we have chosen. For the subject of research we have chosen UTU Falcon arc protection system. It can be considered as a typical industrial safety instrumented system implementing an emergency shutdown function. The purpose of the system is to cut down power feed from an electricity distribution system when an electric arc is detected.

I&C systems are a challenging target domain for model checking. This is because they typically form a closed control loop between their environment, i.e., the controller of an I&C system receives inputs through a feedback loop from its environment. Consequently, in order to verify properties of the system design one has to model also the physical environment to the appropriate extent. This can be difficult because the physical environment typically includes different kinds of continuous quantities and time delays. Especially in the case of safety instrumented systems, the most relevant properties to be verified are often dependent on different kinds of time delays. An option for dealing with these kinds of systems would be to use a real-time model checker which are specifically developed to handle continuous variables [4]. However, in case of safety instrumented systems, where the modelling of environment is often inevitable, the size of the model grows easily too large and model checking becomes infeasible. Therefore, our purpose is to study whether it is possible to model a SIS by using non-real-time model checker NuSMV so that the most relevant properties can be verified. An essential issue in this approach is to find a suitable level of abstraction for handling delays and timing issues.

#### 1.1 Outline of the Report

This work is organised as follows. In Chapter 2 we discuss the existing research made in the field of applying model checking to automation systems. In Chapter 3 we give a concise overview on safety instrumented systems. Moreover, we present an abstract model for safety instrumented systems which captures the overall structure of the systems into which the modelling approach applied with the Falcon system is suitable. In Chapter 4 we describe the NuSMV model checker to the extent that is needed for the reader to be able to follow the rest of the work. Chapter 5 describes how the general parts of the abstract model of Chapter 3 can be modelled by using NuSMV. In Chapter 6 the actual case study is presented, and finally, Chapter 7 draws conclusions on the work.

## 2 MODELS AND ANALYSIS OF CONTROL SYSTEMS

## 2.1 Formal Methods for Digital Automation Systems

In this section we review existing work on applying formal methods to the analysis of digital automation systems. However, as the subject area is very wide, we had to make clear restrictions on the covered topics. Therefore we discuss only studies concerning automation systems based on programmable logic controllers (hereafter PLCs). Consequently, we have mostly excluded systems which are based, e.g., on softPLCs (PLCs based on standard PCs) and distributed control systems (DCSs). This restriction seems reasonable, since the conclusions made on PLCs can be extended to cover also softPLCs. On the other hand, covering also the subject of DCS would have required a survey of a much larger scale. However, the PLC domain can be seen as a logical stepping stone towards analysing of DCS based automation systems. On the method side we are focusing mainly on applying model checking methods to PLC applications.

The analysis of PLC based systems with formal methods can be done on different levels. In the most comprehensive approach the PLC program is verified against the specification of the entire system which consists of the combined specification of the controller and its environment. Another option is to restrict only to verifying the correctness of the controller. In this case the specification of the system as a whole is divided into the specifications of the environment and the controller part, and the program of the controller is analysed with respect to the specification of the controller.

Another classification of approaches on applying formal methods to PLC applications can be made based on the initial objective of the process. That is, the goal might be to analyse an existing application or to design a completely new one. In the first approach an existing PLC program is first transformed into some formal modelling language and then, based on the model, the validation of properties is carried out with a model checker. This approach is often referred to as modelling or formalising existing PLC programs [23]. The related studies are often — but not always — restricted to only validating the controller against its specification. In the second approach a system is designed from the beginning by using a formal modelling method. After the model (which in this case often consists of both, the model of the controller and the environment) is finished, it can be used, alongside of validating properties, to derive a PLC program automatically. This approach is usually referred to as program synthesis [13].

In this study we review studies on both approaches, the modelling of existing PLC programs and the program synthesis. We start by listing some earlier surveys made on the subject. From these we found especially the papers [23, 18] as a good starting point for our own review. After listing already existing surveys we proceed to present references to most relevant studies made on the field up to date. However, before going to the actual survey we give first an overview on PLCs in Section 2.2 and then describe some classification criteria for models of PLC programs in Section 2.3. We use the terminology of the classification framework while describing the references that we list in this work, though not all the referred studies are by no means classified according to all these criteria.

A different version of the survey presented in this work can be found from a technical report prepared for the MODSAFE project [37].

## 2.2 Overview on PLCs

Programmable Logic Controllers (PLCs) are self-contained microcomputers optimised for industrial control [32]. They were introduced in the 1970s as a replacement for control systems based on hardwired circuitry of electromechanical relays. A typical PLC hardware consists of a single microprocessor based CPU, a memory, and input/output-ports through which PLC is connected to sensors and actuators. Typical sources of input data might be e.g., light, current, or heat sensors where as actuators might be e.g., motors or valves. The key characteristic distinguishing PLCs from general microprocessor based systems is their cyclic operation mode. That is, PLC programs are always executed in a permanent loop. A single iteration of the loop is often referred to as a *scan cycle* and it consists of the following three phases: first the input values are read from the sensors, then the program computes a new internal state and output values, and finally the updated output values are passed to the actuators.

Initially, PLCs provided only very restricted functionality comparable to those tasks that could be achieved by using relays. However, since their first appearance to the market the functionality of PLCs has evolved to include many sophisticated features such as multi-tasking, interrupts, watchdogs, etc. Therefore, with respect to the hardware capabilities the difference between PLCs and ordinary PCs is diminishing all the time, and the most fundamental differences to general purpose programming systems lay in the operation mode and the areas of usage of PLCs.

However, with respect to the programming languages, there are huge differences between PLC based systems and general purpose programming systems. The following statements are characteristic to the variety of different PLC languages:

- PLC programming languages tend to be very low-level (this applies especially to languages most applied in the industry), and

- PLC languages have traditionally been vendor specific without conforming to any common standard.

Reasons for this situation are of historical nature. Initially as PLCs were introduced to the market their programming languages were designed to closely resemble the design of hardwired relay circuits. This was done to make the transition to PLC based systems as easy as possible for the control engineers in order to speed up the introduction of the new technique. On the other hand, because PLC based systems are typically designed for a specific industrial target domain, and moreover, the software has initially been only a small part of the whole PLC based system (especially of total design expenses), there has not been as strong demand for fast and constant development of the programming languages and tools as it has been in the case of the general purpose programmable systems [27]. Moreover, even though more evolved programming languages have appeared, the control engineering industry seems to have a tendency of sticking to the most traditional tools.

However, as systems keep getting larger and more complex, and the need for interconnecting industrial systems is increasing, IEC has come up with a common standard IEC 61131-3 for PLC languages. The standard introduces five different languages and it is intended that PLC manufacturers will gradually transform their programming languages to conform to one of languages of the standard. The IEC 61131-3 standard will be discussed more in Section 2.3.

## 2.3 Classification Criteria for PLC Models

Here we describe the three orthogonal criteria for classifying PLC models originally presented by Mader in [23]. The discussion is intentionally kept brief and an interested reader is advised to turn to [23] for more in-depth coverage on the issue.

## Modelling of the Cyclic Operation Mode

The most fundamental characteristic of PLCs is their cyclic operation mode. Therefore the first logical choice in classifying PLC models can be made on the basis of how the scan cycle of the PLC is modelled. There are three possible choices: the scan cycle can be modelled either explicitly or implicitly, or then one can abstract entirely from the scan cycle.

In the explicit modelling of the scan cycle the exact duration of the cycle in actual time units is modelled. Instead, in the implicit modelling the existence of the cycle in itself is modelled, but the actual duration of it is not measured in time units, and moreover, it is considered to be constant. The third option is to abstract from the scan cycle entirely so that the time model of the PLC is considered to be continuous instead of discrete.

## Modelling of Timers

The use of timers is a fundamental characteristic of PLC programs. However, not all of the PLC applications need timers and in many cases the use of them can be avoided, either by modelling techniques or by altering the system design. Therefore, it is justifiable that there are studies concerned with modelling of timers as well as those which abstract from them.

#### The Language Fragment Considered

By the language fragment criterion a choice is made on which parts of the PLC programming language are considered in the modelling process. The first obvious question is which of the five languages defined in the IEC 61131-3 standard is considered. The languages are: Instruction List (IL), Structured Text (ST), Ladder Diagrams (LDs), Function Block Diagrams (FBDs), and Sequential Function Charts (SFCs).

Moreover, usually only a restricted part of the features of the chosen tar-

get language is considered. This is because the IEC 61131-3 standard lacks the definitions of the formal semantics on the languages in standard. Therefore, from the viewpoint of academic research, it simply is not reasonable to consider all possible semantic interpretations of all parts of the languages.

Finally, the language fragment considered can also be restricted on the possible data types, i.e., which of the data types of booleans, integers and real numbers are allowed.

#### 2.4 Survey of Studies on Model Checking PLCs

In this section a survey of studies on applying model checking to PLCs is presented. We start by presenting already existing surveys on the subject in Section 2.4.1 after which we go through studies on modelling of PLC programs in Section 2.4.2. Finally in Section 2.4.3 studies on PLC program synthesis are reviewed.

#### 2.4.1 Previous Surveys

The paper [23] by Angelika Mader presents a classification of different PLC models. It first classifies an orthogonal set of criteria on which PLC models can be classified with. The paper also introduces an extensive list of publications which are classified against the presented criteria. The Doctoral Thesis of Ralf Huuck [18] presents a quite similar survey which includes also more recent studies and a bit extended list of the classification criteria.

The paper [24] also by Mader discusses on a general level applying formal methods to PLC applications. It presents a schema on the structure of a general PLC application and based on this framework analyses the possibilities for applying different formal methods on PLCs.

The paper [43] by Frey introduces four criteria on which studies considering formalisation of existing PLC programs can be categorised. It also presents references to studies falling in each of these categories. The study is by no means as thorough as the survey presented in the papers [23, 18] but contains some additional references and shows another way to classify the existing research.

The paper [13] by Frey presents a general framework on the different phases of verification and validation and discusses what formal methods can be used in these different phases. Therefore, it is not focused only on transforming existing PLC programs to models and it also discusses other formal methods than just model checking.

## 2.4.2 Modelling PLC Applications

In the following we present studies considering the modelling of PLC applications. The references are organised according to the different PLC programming languages.

**Research on modelling SFC programs** The Doctoral Thesis of Ralf Huuck [18] shows how Sequential Function Charts (SFC) programs can be given formal semantics, including a translation of the untimed semantics of PLCs to the Cadence SMV model checker input language. In the paper [3] this research is extended by giving formal semantics also for timed SFCs and in the paper [2] it is shown how timed SFCs can be translated into timed automata. The latter study illustrates in both, timed and untimed cases, the complete verification procedure from model transformation to identifying errors with model checking tools UPPAAL and Cadence SMV.

**Research on modelling IL programs** The widely referred paper [26] by Mader and Wupper shows how a fragment of Instruction List (IL) programs can be translated into timed automata. Based on this study a tool is presented in the paper [39] by Willems which translates IL programs automatically into the timed automata format accepted by UPPAAL model checking tool. This toolchain allows model checking of real time properties with explicit modelling of the scan cycle. The Willems's tool also allows IL programs to contain bounded integer variables. Moreover, UPPAAL tool can be used to model the environment of the PLC as well. In an unpublished paper [22] Mader presents two examples on modelling IL programs and performing their verification with the UPPAAL tool.

In the paper [16] it is shown how IL programs can be transformed into Petri nets. The method allows usage of data structures up to length of 8-bits and it takes into account all standard instructions excluding commands from libraries. However, the real-time aspects are not modelled.

In the paper [15] it is shown how IL programs can be transformed into Timed Net Condition/Event systems. The scan cycle is modelled explicitly and timers are taken into account at some level. However, the possible data structures are restricted to boolean values and only **load**, **store**, **and**, and **or** instructions are considered.

The paper [6] deals with the same fragment of IL programs as the paper [15] described above. In addition, the loop operations are considered. However, [6] is concerned with translating IL programs directly to the input language of the SMV model checker. As SMV cannot directly handle real-time issues, these aspects of the IL program are not analysed.

The paper [21] uses BDD and BMC based symbolic model checkers to model check two small PLC based automation systems written in IL.

**Research on modelling LD programs** In paper [28] Ladder Diagrams (LD) programs are modelled with the SMV model checker without taking timing aspects into account. Based on this study there exists a research paper [34] presenting two comprehensive case studies on existing chemical processing systems. In these case studies also the model of the environment is presented. The verification process revealed numerous faults and the results could be used to improve the designs.

In the paper [31] a large fragment of LD programs are modelled with the SMV model checker. The scan cycle is modelled implicitly and it is shown how a particular type of timers can be modelled in non-real time manner so that certain liveness and safety properties can still be verified.

**Research on modelling ST programs** The paper [19] by Jiménez-Fraustro and Rutten considers of modelling a fragment of the Structured Text (ST)

language with the synchronous language SIGNAL. The fragment includes at least assignments, conditionals and bounded loops. Scan cycles are modelled implicitly and real-time behaviour is not considered. The follow up study [20] considers also the FBD language. Unfortunately, there does not seem to exist any related studies on actual model checking based on the SIG-NAL model.

#### 2.4.3 Methods for Synthesising PLC Programs from Models

In the following we present studies considering the PLC program synthesis.

In the paper [10] Henning Dierks presents a new modelling formalism named PLC-automata especially designed for modelling PLC applications. PLC-automata allows explicit modelling of the scan cycle but it is possible to model only particular type of timers in which an input signal is ignored for a certain time. Dierks shows also how PLC-automata models can be transformed automatically into language of Structured Text.

In the paper [11] it is shown how PLC-automata models can be transformed into timed automata models which makes it possible to perform model checking with a real-time model checker such as KRONOS or UP-PAAL. Moreover, in the paper [33] a tool MOBY/PLC is presented which can be used to modelling PLC-automata, validation, and code generation.

As a continuation for the research based on PLC-automata formalism Olderog presents in paper [29] an approach for designing valid PLC applications. His method is based on formulating design specifications with PLCautomata and specifying requirements in Constraint Diagrams. Olderog also presents a case study from industry for which he applies his approach. In the paper [30] Dierks and Olderog present a tool Moby/RT which is based on the design approach of [29].

A quite interesting research project is reported in the papers [25, 5] by Mader, Brinksma et al. In [25] a systematic design and validation of a PLC control program for a batch plant by using formal methods is reported. This plant was selected as a case study for the EC project on Verification of Hybrid Systems (VHS). In follow up paper [5] it is reported how the SPIN model checker was used for both the verification of a process control program and the derivation of optimal control schedules.

In the paper [41] a Korean research group presents a PLC-based safety critical software development technique for NPP domain. In the method a formal language NuSCR is used for writing software requirement specifications. After a requirement specification is written in NuSCR it can be transformed mechanically into a FBD program (the synthesis phase). The benefit of the method is that NuSCR specifications can be automatically analysed for completeness, consistency, and against the properties specified in temporal logic. Moreover, NuSCR specification language was developed during the research project together with NPP domain experts and it was designed to especially suit the needs of nuclear engineering domain. NuSCR specification language is explained more closely in the paper [42] and the paper [40] describes more thoroughly the process of synthesising FBD programs from NuSCR specifications. The paper [8] presents NuEditor tool which can be used for creating NuSCR specifications and performing con-

8

sistency and completeness analysis on the specifications. NuEditor can also be used to translate a NuSCR specification into SMV input so that model checking of safety and liveness properties can be performed on the specification. However, NuEditor cannot be used for synthesising FBD programs from specifications and, apparently, for this task there does not yet seem to exist any tool support. The paper [8] presents also a case study in which a reactor protection system for Korean nuclear power plant was specified with NuEditor and verified against safety and liveness properties with SMV model checker.

## 2.5 Overall Status of the Research on Model Checking PLCs

On the study field of modelling PLC programs most research papers seem to be available on the language of Instruction List. On Ladder Diagram programs there is also quite a lot research but, still, on this area there seems to be many gaps to be filled, especially on covering timers and real time issues. Instead, in the case of the SFC programs the situation is quite opposite: there hasn't been that many research projects but the existing ones are actually quite covering.

Considering the last two languages of the IEC 61131-3 standard, i.e., on Structured Text and Function Block Diagrams, there seems to exist only very few studies. We presume that the reason for this in the case of the ST language might be that the relevant problems on the modelling issues are present also in the IL language which in its brevity suits better academic research. Instead, in the case of the FBD language, the similar but more evolved SFC language provides features not existing in FBD, and therefore, might be more appealing target for the research.

For the synthesising approach there has also clearly been quite a lot of research activity. The usefulness of this type of an approach has especially been shown in the Korean research project which was described above. This project has proven that the synthesis approach can be successfully applied in producing real application programs in the NPP I&C domain. Moreover, the project was also successful in producing a formal specification language which was readily accepted by domain experts.

## **3 SAFETY INSTRUMENTED SYSTEMS**

#### 3.1 Overview on Safety Instrumented Systems

Safety Instrumented System (SIS) is used to implement safety related functions on industrial systems or processes [14]. They consist of sensors, logic solvers, and final elements. Typical uses for a SIS are shutdown functions and permissive functions. In shutdown functions a protected system or a process is taken to a safe state if a hazardous event or condition is met. In case of a permissive function the purpose is the opposite: a process is permitted to move forward when specified conditions are met.

Regardless of the specific safety function implemented, a SIS operates by monitoring process variables of the protected system and it only initiates action if the variables reach specified threshold values. If the threshold values are reached, SIS performs the specified safety function by operating final elements such as switches, valves, or breakers of the protected system. It should be noted here that the final elements of a SIS are typically physical parts of the protected system, i.e., terminologically they belong to both of them.

### 3.2 An Abstract Model of Safety Instrumented Systems

In this section we present an abstract model of safety instrumented systems which characterises the systems which our model checking method can be applied to. Further in Section 5 we present the general overview of our model checking method with the aid of this model.

Our model is very general in a sense that it doesn't make any restrictions nor assumptions on the protected system or the specific safety function implemented by SIS. However, as our model does not allow the logic solver to be arbitrary, it cannot be seen as a generic model of all possible SISs.

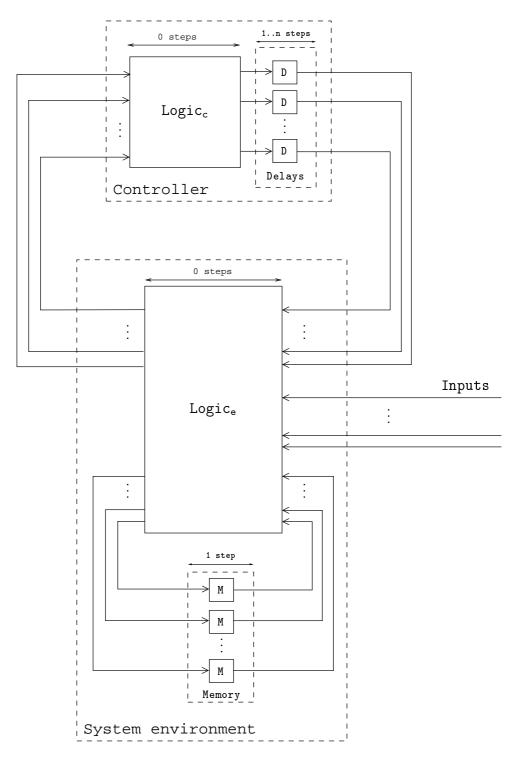

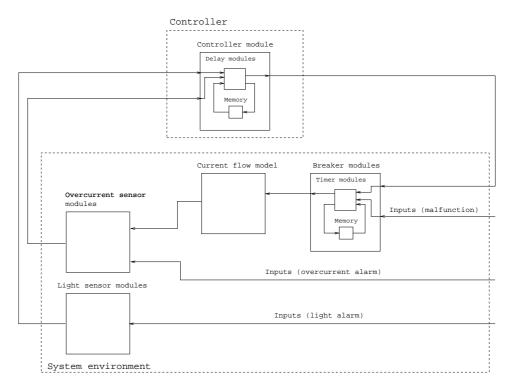

The abstract model is shown in Figure 1 and described in the following.

## Overall description of the model

The model describes a SIS with its environment and the closed control loop between them. Model is divided into two parts, into Controller and System environment. Controller models only the logic solver of a SIS. The model assumes that the logic solver is based on a controller with cyclic operation mode and constant length scan cycle (see Section 2.2 for description of scan cycle). System environment is an abstraction of the sensors and the final elements of a SIS as well as the protected system. It should include all the parts of the physical environment which might affect the operation of the SIS. The arrows from System environment to Controller and Controller to System environment represent the signals from sensors to the logic solver of a SIS and the signals from logic solver to the final elements of a SIS, respectively. The values of the signals are binary, i.e., at any given moment the value of each signal is either 0 or 1. The control loop is closed as Controller affects the state of the protected system by controlling the final elements and the sensor data received by Controller depends on the state of the protected system.

Figure 1: An abstract model of a SIS

The model abstracts physical devices with both discrete and continuous behaviour. However, as the operation mode of the logic solver of the SIS is assumed to be cyclic with constant scan cycle, it interacts with the environment only on discrete instants. Therefore, the transient states of the system, that is, the states between starting and ending points of a scan cycle, are irrelevant with respect to the control logic of the logic solver. For this reason the time model of the whole system can be considered discrete so that the values of signals and state variables are updated only on discrete time steps. The unit time step of the model represents a single scan cycle of the logic solver of the SIS.

#### **Description of Controller**

Controller abstracts logic solver of a SIS into Logic<sub>c</sub> and Delays parts. Logic<sub>c</sub> part represents the control logic of the modelled SIS, i.e., it specifies the logical rules on how the SIS reacts to each combination of input signals. In the model Logic<sub>c</sub> part is modelled as a logical function which calculates outputs as a function of input values instantaneously without any time delay.

Delays of Controller represent a specific type of delays commonly used with SISs. The delay gates of Delays part are associated with a delay length parameter (number of time steps) and they operate in such a way that a delay gate only gives an output signal 1 if it has received a non-stop input signal for a time period specified with the parameter of that delay. Otherwise the output signal is 0. These kinds of delays can be used with SISs to eliminate too hasty reactions by ensuring that the alarm condition remains for a certain time before an action is taken. In our model the scan cycle of the controller of a SIS is also included into Delays. For this reason it takes always at least one time step for a signal to go through Delays part.

We define the state of Controller as the set of the input signals of Controller, the input signals of Delays (obtained as the results of  $\text{Logic}_c$  acting on input values), the internal state of the delay gates of Delays part, and the outputs of Controller. The internal state of a single delay gate can be seen as an integer number in the value range 0..*delay* where the *delay* stands for the delay parameter of the gate. The purpose of the states of the delay gates is to keep track of the number of consecutive 1-valued signals up to number of scan cycles specified by the delay parameter.

#### Description of System environment

System environment abstracts the physical elements it represents into Logic<sub>e</sub>, Inputs, and Memory parts. Inputs represent events which affect the system but whose cause or origin cannot be modelled. Most importantly this means events which are caused by emergency situations and perceived by sensors. Inputs can also be used to represent malfunctions in physical devices, for instance. As it is with the input and output signals of Controller, Inputs are expected to be binary valued.

$Logic_e$  part represents the operational model of the physical devices included in System environment and the interaction between them. Basically  $Logic_e$  specifies how the control signals of Controller and Inputs of System

environment affect the input signals of Controller. Part of the interactions between physical devices can be seen as instantaneous. For instance, depending on the situation an electricity feed might be considered to be cut down instantaneously at the moment it is switched off. On the other hand, some interactions might not be instantaneous but happen with a delay. For instance, for a valve it might take a considerable amount of time to close a pipe after it has received a launch signal. Moreover, effects of an interaction (either delayed or instantaneous) might also depend on the current state of System environment and/or they might change the state of System environment. For these reasons System environment contains Memory part whose memory elements can be used to store such variables whose values in a given time step are determined in the previous time step. We define the state of System environment in a given time step as a set of values which includes the predetermined variables stored in Memory, Inputs of System environment, the output signals from Controller, and the effects of instantaneous interactions determined by Logice part.

System environment works so that on each time step Logic<sub>e</sub> part counts the effects of interactions as a logical function of the output signals of Controller, Input of System environment, and the outputs from Memory part. That is, the model is designed so that regardless of the type of the interaction (instantaneous or delayed) the result is calculated immediately without a time delay. Therefore, the effects of the instantaneous interactions happening in a certain time step can be seen at the same time step. However, in case of the delayed interactions, the result is not shown immediately but it is stored in the memory element, which shows the result only in the following time step. If an interaction happens with longer delay than one time step, it can be modelled simply by iteratively storing the result into a memory element until the corresponding time delay has elapsed.

## 3.3 Classification of the Abstract SIS Model

In Section 2.3 we presented a coarse framework with three orthogonal criteria for classification of PLC models. The first criterion specifies how the scan cycle of a PLC is modelled. In our case the modelling is done implicitly, i.e., the existence of scan cycle is modelled but its length is assumed to be constant. Moreover, the time length of the scan cycle is not modelled but it is taken to be the unit time step of the SIS model.

The second criterion simply divides PLC models to two classes based on whether they model timers or do not. Thus, our model falls into the class in which timers are modelled.

Finally, the third criterion makes distinction on the models on the basis of which programming language of the IEC 61131-3 standard is used. With this respect our model cannot be classified as it describes SIS on an abstract level. On behalf of our model, any of the five languages of the IEC 61131-3 standard could be used to implement the control logic of the logic solver of a SIS. However, the language used in the case study of Section 6 resembles closest to a very limited subset of the Function Block Diagrams language.

## 4 MODELLING AND ANALYSING SYSTEMS WITH NUSMV

In this section we describe the NuSMV model checker [1] which was used in the Falcon case study. Section 4.1 gives a general overview of NuSMV, Section 4.2 describes how models are build with the input language of NuSMV, and Section 4.3 describes how verified properties are specified with the input language of NuSMV. The discussion on the syntax and semantics of the input language of NuSMV covers only the parts of the language which are used in this study. For further information we advise the reader to see the NuSMV user manual [7].

## 4.1 General Overview

NuSMV is a symbolic model checker developed by ITC-IRST. NuSMV can be used to describe finite state systems that range from completely synchronous to completely asynchronous. The main reason for choosing NuSMV was that it is a state-of-the-art model checker which has proven to be capable of handling industrial-sized systems. Moreover, NuSMV supports both BDD (Binary Decision Diagram) and SAT<sup>1</sup> (propositional satisfiability) based model checking which are currently the main approaches in implementing symbolic model checking tools. Being distributed under an OpenSource licence, NuSMV also offers a promising platform for research purposes.

## 4.2 Modelling with NuSMV

## 4.2.1 General Structure of NuSMV Models

NuSMV models (also referred to as NuSMV programs) consist of one or more *module declarations*. A module declaration is an encapsulated collection of declarations, constraints, and specifications. Intuitively, the idea of the module concept is to encapsulate closely related state variables together in order clarify the structure of the whole model. Modules are used in such a way that a module declaration is used as a variable type to create *module instances*. Therefore, multiple realisations of a module can be created based on a single module declaration. A module declaration may contain instances of other modules so that the modules form a hierarchical structure. Each NuSMV model is built on a declaration of a special module which has to be named as main.

Next we describe the basic constructs needed for creating module declarations. The description is based on the NuSMV model shown in Figure 2, which has two module declarations. The model is complete and it introduces all structures used in our actual case study.

## 4.2.2 Structure of a Module Declaration

14

A description of a NuSMV module consists of several different segments containing different kinds of declarations, specifications, and constraints. In this

<sup>&</sup>lt;sup>1</sup>Some of the SAT based model checking algorithms inside NuSMV have been developed at TKK/ICS [17].

```

MODULE exampleModule(param1,param2)

VAR

var1 : boolean;

var2 : -1 .. 10;

var3 : -1 .. 2;

ASSIGN

-- An example of direct assignment.

var1 := (var2 > 1);

-- An example of assignment with init/next-construct.

init(var2) := 0;

next(var2) := param1 + param2;

-- An example of assignment with init/next-construct

-- with a case expression.

init(var3) := -1;

next(var3) :=

case

(var3 < 2) : var3 + 1;

(var3 = 2) : \{0,2\};

esac:

MODULE main()

VAR.

moduleInstance : exampleModule(definedConstant, 5);

DEFINE

definedConstant := 1;

_____

-- Specification of properties

LTLSPEC G (moduleInstance.var1 -> 0 (moduleInstance.var2 = 10))

LTLSPEC F (moduleInstance.var2 > moduleInstance.var3)

```

Figure 2: An example of a NuSMV model

case study, only the most central constructs were needed. These include the parameters of modules, the declaration and assignment of state variables, and define declarations. These are described in the following.

**Parameters of a module.** Parameters are defined as a list of identifiers which can be used for passing data to a module from other modules. The parameters of a module are specified with a parenthesised list of identifiers following the name of a module (see param1 and param2 in the example above). The main module is not allowed to have parameters.

**State variables of a module.** The state variables of a module are listed in a segment identified with the keyword VAR. A state variable declaration consists of an identifier which can be used to refer to the variable and a type specification which describes the data type and the range of possible values of the variable. As data types one can use either built-in data types or module declarations.

In our case study, only two built-in data types, boolean and integer, are

used. The boolean data type comprises two integer values, 0 and 1 (or their symbolic counterparts false and true respectively.) The value range of the integer type consists of integer values from  $-2^{31}$  to  $2^{31} - 1$ . The integer type is specified by declaring a value range after the variable identifier (see declaration of var2 in the exampleModule.)

If a module declaration is used as a data type in a variable declaration, the variable is said to be an instance of the module, and the variable declaration is said to be a module instantiation. The declaration is formed simply by referring to the module name (followed by a list of parameters) in the place of the variable type (see variable moduleInstance in the main module in Figure 2.)

Assignment of state variables. State variables are assigned in a segment identified with the keyword ASSIGN. A state variable can be assigned in two distinct ways, either directly or with an init/next construct. The variable var1 in the exampleModule in Figure 2 shows an example of direct assignment. In this case, the value of the current value of the var1 is set to the value of the expression (var2 > 1) by using the current value of the var2 at all time steps.

In the case of the variable var2 in the exampleModule, the assignment is done using the init/next construct. In this case, the assignment is done in two steps: first the *initial* value (i.e., the value of the state variable at the first time step, or in the initial state) of var2 is set to zero. On the following line, it is stated that the value of var2 in the *next* state will be the value of param1 + param2.

The variable var3 in the exampleModule is also assigned with an init/ next construct but in its next-expression another two important constructs related to assignments are shown: the *case expression* and the *set expression*. The segment surrounded by keywords case and esac defines a case expression. It can be used to express how the value assigned to a state variable depends on the condition of other state variables. Each line of the case segment has on its left-hand side a boolean valued condition statement and on its right-hand side a value which is assigned to the state variable if the condition holds. The lines are evaluated sequentially one-by-one starting from the first line until the first line whose condition part is non-zero is reached. NuSMV requires the conditions of a case expression to be exhaustive, that is, there has to be always at least one line whose condition part evaluates to a non-zero value.

In the case of var3, the case statement increases its value in the next state by one if the current value is below the value 2 (which is the maximum value it can have). If the current value of var3 is 2, its value in the next state is chosen randomly from the set expression  $\{0, 2\}$ . Set expression lists the possible values one by one, so in this case the possible values are 0 and 2. The purpose of the set expressions is discussed in Section 4.2.3.

**DEFINE declarations.** Define declarations are yet another basic construct used to build modules. Define declarations are added in a module declaration after the keyword **DEFINE** and they are used to associate a common expression with a symbol. That is, the define declarations are used to define

shorthands for complex expressions or numeric values in order to make module descriptions more concise. The defineConstant of the main module in Figure 2 shows an example of define declaration in which the numeric value 1 is associated with the identifier in question.

## 4.2.3 Semantics of NuSMV Models

When restricted to the features of NuSMV that are used in this study, NuSMV models represent a finite state machine (FSM), i.e., a structure with a finite set of states, a total transition relation between the states, and a set of possible initial states. A state of a NuSMV model is an assignment of values to the state variables of the model. Thereby, the number of different potentially reachable states specified by a NuSMV model equals the number of the possible value assignments of the state variables of the model. The set of all states of a NuSMV model is referred to as the state space of the model. The updating of the values of the state variables of a NuSMV model according to their assignment specifications is referred to as a transition from a state to another. The possible transitions of the FSM can be specified by the transition relation that relates a set of states to each state. By an initial state we mean the first assignment of values to the state variables of the model when the model checking process is started. NuSMV allows defining different possible initial states by using the set expressions described in Section 4.2.2. If the model allows more than one possible initial state, we say that the model has a nondeterministic initial state or that the initial state of the model is chosen nondeterministically.

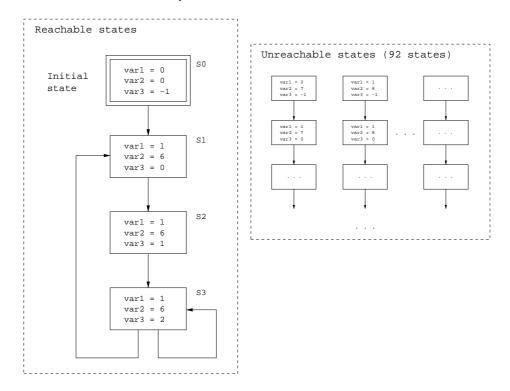

A finite state machine can be represented graphically with a state transition diagram. In Figure 3, a state transition diagram of the example NuSMV model of Figure 2 is shown. The boxes in the figure represent the possible states and the arrows between boxes represent the possible transitions between states. If a state belongs to the set of initial states, it is depicted with a double-stroke box.

For model checking, the possible executions of the finite state machine specified by a NuSMV model are of central interest. By an execution we mean an infinite path  $\pi = s_0 s_1 \dots$  of states where the states of the path belong to the state space of the NuSMV model, the initial state of the path belongs to the set of possible initial states of the model, and the transitions between consecutive states on the path are allowed by the transition relation of the model.

A NuSMV model allows more than one kind of an execution if the initial state of the model is nondeterministic or if the transition relation of the model is nondeterministic. The transition relation is nondeterministic if it relates a set of states with more than one state to at least one state of the model. In other words, the transition relation of a model is nondeterministic if it allows more than one transition from at least one of the states of the model. In our example model, the transition relation is nondeterministic as it allows transition from state S3 to S1 as well as a transition from the state S3 to the state S3 itself.

A state of a NuSMV model is *reachable* if the state belongs to any of the possible executions of the model. The state space of our example model

consists of 96 states in total but from these only four are reachable. There might also be legal transitions starting from an unreachable state and ending to any of the states of the model but as long as an execution starts from one of the initial states of the system, such transitions cannot ever be taken.

Figure 3: State diagram of the running example

## 4.3 Specifying Properties with NuSMV

The properties of this study are specified by using Linear Temporal Logic extended with past operators (hereafter PLTL). Also invariant specifications are used, but they can be formulated in PLTL as well. In this section we describe the syntax of PLTL in NuSMV.

In NuSMV, PLTL formulas are used to specify conditions or relations between *atomic propositions* of a NuSMV model. Atomic propositions are boolean valued expressions formed by connecting state variables with comparison operators  $\{<, >, \leq, \geq, =\}$ . An atomic proposition consisting of a single non-boolean variable is interpreted as a boolean variable so that the value 0 is interpreted as the boolean value false and all non zero values are interpreted as the boolean value true. PLTL formulas are formed by connecting atomic propositions with boolean operators and special *temporal* operators which can be used to specify time related statements. In this context, time is interpreted as the indexing of states of an execution. That is, the *N*th state of an execution is considered as the state of the system in the *time step N*. Consequently, temporal operators are used, strictly speaking, to specify properties related to the executions of a NuSMV model.

The following list contains the logical operators used in this study<sup>2</sup> in the

18

<sup>&</sup>lt;sup>2</sup>More extensive coverage of PLTL with past operators can be found in the NuSMV user

syntax of NuSMV and describes their semantics informally. In the following section, it is shown how the semantics of these operators is defined formally.

Boolean operators in the NuSMV syntax:

!x (logical not): !x is true if x is not true.

x & y (logical AND): x & y is true if x is true and y is true.

$x \mid y$  (logical OR):  $x \mid y$  is true if x is true or y is true.

$\rightarrow$  (implication):  $x \rightarrow y$  is true if y is true whenever x is true.

$\leftrightarrow$  (equivalence):  $x \leftrightarrow y$  is true if the values of x and y are equal.

Temporal operators in the NuSMV syntax:

G (globally): G f is true if f is true at all time steps.

- F (finally): Ff is true at this time step if f will be true at some time step in the future.

- O (once): O f is true if f is true at this time step or has been true at some previous time step.

- Y (previous state): Y f is true if f was true at previous time step.

In the example model of Figure 2, two examples of PLTL property specifications are shown. The first property states that "in all time steps it holds that if the value of var1 of moduleInstance is true, then there has to be a time step in the past in which the value of var2 of moduleInstance was 10". The second property states that "there has to be some time step in which it holds that the value of var2 of moduleInstance is bigger than the value of var3 of moduleInstance."

## 4.3.1 Semantics of PLTL formulas

In the following, the formal semantics of PLTL formulas is given. The semantics is defined along the executions of a NuSMV model. Each state  $s_i$ of an execution  $\pi = s_0 s_1 \dots$  is associated with a set of atomic propositions which evaluate to the value **true** in that state. This is expressed with a labelling function  $L(s) \in 2^{AP}$  where AP is the set of all atomic propositions of the NuSMV model and s is a state of the NuSMV model.

**Definition 1** (PLTL semantics.). Let  $\pi$  be an execution of a NuSMV model and h, f and g be PLTL formulas so that f and g are subformulas of h. Moreover, let  $\pi(i)$  denote the state  $s_i$  along a path  $\pi$ . Then  $\pi \models h$  (h is valid along

manual [7] or in the paper [17] by Heljanko, Junttila, and Latvala.

$\pi$ ) iff  $\pi^0 \models h$ , where:

| $\pi^i \models p$           | iff $p \in L(\pi(i))$ for $p \in AP$ .           |

|-----------------------------|--------------------------------------------------|

| $\pi^i \models \neg f$      | iff $\pi^i \not\models f$ .                      |

| $\pi^i \models f \lor g$    | iff $\pi^i \models f$ or $\pi^i \models g$ .     |

| $\pi^i \models f \land g$   | iff $\pi^i \models f$ and $\pi^i \models g$ .    |

| $\pi^i \models \mathbf{G}f$ | iff $\pi^j \models f$ for all $j \ge i$ .        |

| $\pi^i \models \mathbf{F}f$ | iff $\pi^j \models f$ for some $j \ge i$ .       |

| $\pi^i \models \mathbf{O}f$ | iff $\pi^j \models f$ for some $0 \le j \le i$ . |

| $\pi^i \models \mathbf{Y}f$ | iff $i > 0$ and $\pi^{i-1} \models f$ .          |

The definition above describes the meaning of a PLTL formula with respect to a single execution of a NuSMV model. In contrast, the following definition describes the meaning of a PLTL formula in the context of a whole NuSMV model.

**Definition 2** (Validity of a PLTL formula.). A PLTL formula f is valid in a NuSMV model M (denoted as  $M \models f$ ) iff  $\pi \models f$  for all executions  $\pi$  in M.

With these definitions, the model checking with NuSMV can be described as the process of deciding whether given PLTL formulas are valid in a given NuSMV model. Moreover, an essential function of the NuSMV model checker is to return a *counter example* for each PLTL formula that is not valid. A counter example for a PLTL formula is an execution of a NuSMV model along which the formula is not valid.

## 5 MODELLING SAFETY INSTRUMENTED SYSTEMS WITH NUSMV

In this chapter we give general guidelines on how a safety instrumented system compatible with the abstract model of Section 3.2 can be modelled using the NuSMV modelling language. Section 5.1 covers the Controller and Section 5.2 covers the System environment of the abstract model.

#### 5.1 Modelling the Controller

In NuSMV, Controller of the abstract model (see Figure 1) can be modelled by defining two modules: one encodes Delays part and the other one encodes the whole Controller by using instances of the Delay module as building blocks. In the following we describe the overall structure of these modules.

#### 5.1.1 Implementation of the Delay module

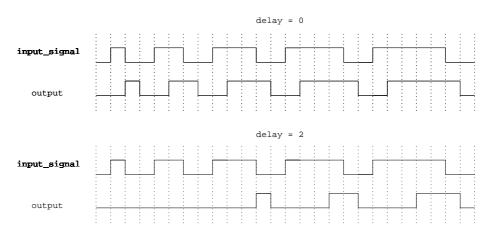

Figure 5 shows how the Delay module can be implemented. The module has two parameters: boolean valued input signal (named as input\_signal) and a delay value (named as delay) whose type is a non-negative integer (it should be noted here that NuSMV does not allow explicit type declarations for module parameters but type checking is carried out implicitly). The module has a boolean valued variable named as output which represents the output signal of the abstract delay.

The operation logic of the module can be stated as follows. On a given time step  $t_n$ , the value of the output variable is set to 1 if and only if the value of the input\_signal has been 1 on the previous consecutive time steps  $t_{n-(delay+1)}, \ldots, t_{n-1}$  where delay is the value of the delay parameter. That is, the value of the input\_signal parameter in time step  $t_n$  does not affect the value of the output in the time step  $t_n$ . Moreover, if the value of the delay parameter is 0, the value of the output variable depends only on the variable of the input\_signal parameter in the previous time step  $t_{n-1}$ . The operation logic of the Delay module is illustrated in Figure 4.

Figure 4: Input/output behaviour of the Delay module

The operation logic of the Delay module is implemented by using an integer valued counter variable (named as count) whose values may vary

between 0 and the value of the sum delay + 1. The value of the count is set to 0 whenever the input\_signal parameter is 0. If the value of the input\_signal parameter is 1, the value of the count is increased until it reaches the value of the sum delay + 1 (here the sum delay + 1 is used instead of delay because the total delay corresponds to the delay caused by the delay gate plus the unit delay caused by the scan cycle of the Controller, see Section 3.2.) After this the value of the count remains unchanged until the input\_signal value 0 is received.

The value assignment of the output variable is specified so that it will be l in a given time step if (and only if) the count has reached the value of the delay parameter in that time step (this is achieved by referring to the value next(count) instead of count in the assignment specification of the output variable.) Otherwise the value of the output is set to the value 0.

```

MODULE Delay(input_signal, delay)

VAR

count : 0..DELAY_RANGE_UPPER_LIMIT;

output : boolean;

DEFINE

-- Total delay consist of the delay + scan cycle

total_delay := delay + 1;

ASSIGN

init(count) := 0;

next(count) :=

case

input signal = 0

: 0;

count >= total_delay : count;

: count + 1;

1

esac;

init(output) := 0;

next(output) :=

case

-- At the step when count = delay, output has to be 1.

next(count) >= total_delay : 1;

: 0:

1

esac;

```

Figure 5: Implementation of the Delay module

#### 5.1.2 Implementation of the Controller module

Figure 6 shows an outline for the implementation of the Controller module which corresponds to the Controller part of the abstract model (referred to as the abstract Controller from here on). The Controller module has a boolean valued parameter for each input signal *i* of the abstract Controller (named as input\_i). For each output signal *j* of the abstract Controller the Controller module has two define declarations named as logic\_output\_j and controller\_output\_j, and an instance of the Delay module named as delay\_gate\_j. Each define declaration logic\_output\_j is defined as a function of the parameters of the Controller module. Thus, these functions encode the Logic<sub>c</sub> part of the abstract model. Each define declaration logic\_output\_j is passed as an input signal parameter to the Delay module instance delay\_gate\_j (see parameter input\_signal in the implementation of the Delay module). Finally, each define declaration controller\_output\_j is set to the value of the output variable of the Delay module instance delay\_gate\_j. Consequently, the declaration controller \_output\_j corresponds to the output value j of the Controller.

The delay parameter values of the Delay module instances (see e.g., delay \_param\_1 in Figure 6) are set to values  $\lceil D/t \rceil$  where D is the delay in milliseconds of the corresponding delay gate in the modelled system and t is the length (also measured in milliseconds) of the scan cycle of the controller of the modelled system.

Figure 6: An outline for the implementation of the Controller module

## 5.2 Modelling the Environment

As it was described in Section 3.2, the purpose of the System environment of the abstract model (see Figure 1) is to capture all the relevant parts of the physical environment of a SIS and the interactions between them. In the abstract model the logical rules of the interactions are represented with Logic<sub>e</sub> part. In NuSMV, Logic<sub>e</sub> is implemented by specifying logical functions on the variables of the NuSMV model. As specified by the abstract model, the results of the instantaneous interactions are shown immediately at the same time step that they are calculated. This can be implemented in NuSMV by assigning the results of the corresponding functions to define declarations. For an example see the define declaration electricity\_feed\_off in Figure 7.

On the other hand, the abstract model specifies that in the case of the delayed interactions the results of the interactions are stored in the Mem-

ory and they are shown only after one scan cycle. In NuSMV this can be implemented by assigning the results of the corresponding functions to state variables by using the init/next-construct. For an example see the variable circuit\_breaker1\_cuts in Figure 7.

```

VAR

water_boiler_is_empty : boolean;

-- Timer for water_boiler_empty variable

-- (using delay of 5 time steps.):

timer : Timer(valve1_closed & valve2_closed, 5);

circuit_breaker1_cuts : boolean;

. . .

DEFINE

electricity_feed_off :=

circuit_breaker1_cuts | circuit_breaker2_cuts;

ASSIGN

init(circuit_breaker1_cuts) := 0

next(circuit breaker1 cuts) :=

case

(circuit_breaker1_launched = 1) : 1;

(circuit_breaker1_launched = 0) : 0;

esac;

water_boiler_empty := timer.output;

```

Figure 7: Implementation of  $\operatorname{Logic}_{\operatorname{e}}$  and Memory parts of the abstract SIS model

Often the delay of an interaction might be longer than one scan cycle. Longer delays can be handled by implementing a certain type of a timer module which, informally, holds a given value for the number of scan cycles specified with a parameter value. In practice, instead of assigning the result of a function implementing the logic of an interaction to a state variable, the result is passed to an instance of a timer module which, informally, holds the value for the specified time before making it available. This is demonstrated with the variable water\_boiler\_empty in Figure 7. In the end of this section we show how to implement this kind of a timer module.

The inputs of the system can be fully independent of the system or they can depend either on the current state of the system (e.g., a short-circuit cannot occur if the electricity feed is down) or the previous state of the system (e.g., a device cannot break down if it is already broken.) Either way, in NuSMV an unconstrained input can be implemented by assigning a set expression  $\{0, 1\}$  to a boolean state variable. The value 0 of the set expression at a time step implies that the event corresponding to an input does not occur at that time step and the value 1 implies that the event does occur at the time step.

Figure 8 shows an example on how inputs can be implemented in NuSMV. If an input is fully independent of the system the assignment can be done directly (see the it\_is\_raining\_outside variable.) If an input depends on the current state of the system it can be done by using a direct assignment

with a case expression (see the short\_circuit variable.) Finally, if an input depends on the state of the system in the previous time step then the assignment is done by using an *init/next* construct and the case expression (see the device\_is\_broken variable.)

With respect to implementing the inputs, one might want to use define declarations in the place of the variables and direct assignment. However, this is not possible because NuSMV does not allow to use set expressions in the define declarations.

VAR it\_is\_raining\_outside : boolean; short\_circuit : boolean; device\_is\_broken : boolean; . . . ASSIGN it\_is\_raining\_outside := {0,1}; short\_circuit := case (electricity\_feed\_on = 0) : 0;  $(electricity_feed_on = 1) : \{0,1\};$ esac; init(device is broken) := {0,1}; next(device is broken) := case (device\_is\_broken = 1) : 1; (device\_is\_broken = 0) : {0,1}; esac:

Figure 8: Implementation of the Inputs of the abstract SIS model

#### 5.2.1 Implementation of the Timer module

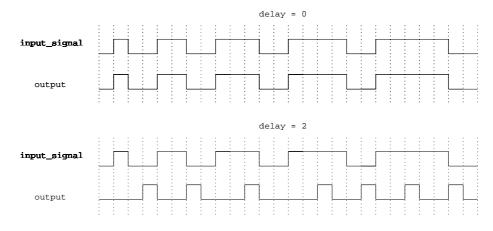

Figure 10 shows an implementation of the Timer module. The module has the same parameters as the Delay module described above: a boolean valued input signal and a delay value whose type is a non-negative integer. These are named as input\_signal and delay, respectively. It also defines the output signal (named as output) as a boolean valued variable. The operation logic of the Timer module is described as follows. In the basic state the module is waiting for an input signal, i.e., it is waiting for that value 1 is passed through the input\_signal parameter. When this happens the module will be in the *waiting state* for the number of time steps specified by the delay parameter. After this the module transfers automatically into the *launch state* in which it will stay only for one time step. In the launch state the value of the output variable is set to 1 (in the other states it is 0). After staying in the launch state for one time step, the module automatically transfers back into the waiting state. The value of the input\_signal parameter is ignored whenever the module is not in the basic state. The operation logic of the Timer module is illustrated in Figure 9.

As in the case of the Delay module, the implementation of the Timer

Figure 9: Input/output behaviour of the Timer module