## Helsinki University of Technology Laboratory for Theoretical Computer Science Research Reports 81

Teknillisen korkeakoulun tietojenkäsittelyteorian laboratorion tutkimusraportti 81

Espoo 2003 HUT-TCS-A81

# EFFICIENT COMPUTER-AIDED VERIFICATION OF PARALLEL AND DISTRIBUTED SOFTWARE SYSTEMS

Marko Mäkelä

TEKNILLINEN KORKEAKOULU

TEKNISKA HÖGSKOLAN

HELSINKI UNIVERSITY OF TECHNOLOGY

TECHNISCHE UNIVERSITÄT HELSINKI

UNIVERSITE DE TECHNOLOGIE D'HELSINKI

## Helsinki University of Technology Laboratory for Theoretical Computer Science Research Reports 81

Teknillisen korkeakoulun tietojenkäsittelyteorian laboratorion tutkimusraportti 81

Espoo 2003 HUT-TCS-A81

# EFFICIENT COMPUTER-AIDED VERIFICATION OF PARALLEL AND DISTRIBUTED SOFTWARE SYSTEMS

#### Marko Mäkelä

Dissertation for the degree of Doctor of Science in Technology to be presented with due permission of the Department of Computer Science and Engineering, for public examination and debate in Auditorium E at Helsinki University of Technology (Espoo, Finland) on the 28<sup>th</sup> of November, 2003, at 12 o'clock noon.

Helsinki University of Technology Department of Computer Science and Engineering Laboratory for Theoretical Computer Science

Teknillinen korkeakoulu Tietotekniikan osasto Tietojenkäsittelyteorian laboratorio

#### Distribution:

Helsinki University of Technology Laboratory for Theoretical Computer Science P.O.Box 5400 FIN-02015 HUT Tel. +358-0-451 1

Fax. +358-0-451 3369 E-mail: lab@tcs.hut.fi

## © Marko Mäkelä

ISBN 951-22-6791-8 ISBN 951-22-6792-6 (PDF) ISSN 1457-7615

Otamedia Oy Espoo 2003 ABSTRACT: The society is becoming increasingly dependent on applications of distributed software systems, such as controller systems and wireless telecommunications. It is very difficult to guarantee the correct operation of this kind of systems with traditional software quality assurance methods, such as code reviews and testing. Formal methods, which are based on mathematical theories, have been suggested as a solution. Unfortunately, the vast complexity of the systems and the lack of competent personnel have prevented the adoption of sophisticated methods, such as theorem proving.

Computerised tools for verifying finite state asynchronous systems exist, and they been successful on locating errors in relatively small software systems. However, a direct translation of software to low-level formal models may lead to unmanageably large models or complex behaviour. Abstract models and algorithms that operate on compact high-level designs are needed to analyse larger systems.

This work introduces modelling formalisms and verification methods of distributed systems, presents efficient algorithms for verifying high-level models of large software systems, including an automated method for abstracting unneeded details from systems consisting of loosely connected components, and shows how the methods can be applied in the software development industry.

**KEYWORDS:** distributed systems, software systems, model checking, verification, reachability analysis

# Contents

| Pı            | retac                  | е                                                  | 1   |

|---------------|------------------------|----------------------------------------------------|-----|

| $\mathbf{Li}$ | $\operatorname{st}$ of | Publications                                       | 2   |

| 1             | Intr                   | roduction                                          | 3   |

| _             | 1.1                    |                                                    | 4   |

|               | 1.2                    | v                                                  | 5   |

|               |                        |                                                    |     |

|               | 1.3                    | Contributions                                      | 6   |

| 2             | Ver                    | ification                                          | 8   |

|               | 2.1                    | Formulating and Checking the Desired Properties    | 9   |

|               | 2.2                    | Modelling Formalisms                               | 0   |

|               |                        | Guarded Command Languages                          |     |

|               |                        | Process Algebra                                    |     |

|               |                        | Transition Systems                                 |     |

|               |                        | Petri Nets                                         |     |

|               |                        |                                                    |     |

|               | 0.0                    | 8                                                  |     |

|               | 2.3                    | Specialised Verification Methods and Tools         |     |

|               |                        | Theorem Proving                                    |     |

|               |                        | Rewriting Systems and Equivalence Tests            |     |

|               |                        | Structural Analysis                                |     |

|               |                        | Symbolic Model Checking                            | 7   |

| 3             | Stat                   | te Space Enumeration 1                             | O   |

| J             | 3.1                    | Benefits of State Space Enumeration                |     |

|               |                        |                                                    |     |

|               | 3.2                    | Alleviating the State Space Explosion              |     |

|               |                        | Eliminating Redundant Data                         |     |

|               |                        | Dealing with Independent Actions                   |     |

|               |                        | Compositional Verification                         |     |

|               | 3.3                    | Reducing the Memory Usage                          | .2  |

|               |                        | Relaxing the Loop Check                            | .2  |

|               |                        | Compression Techniques                             | 3   |

|               |                        | Approximating the Set of Reachable States          | 4   |

|               | 3.4                    | Reducing the Execution Time                        |     |

|               |                        | 0                                                  |     |

| 4             | Dev                    | veloping Verified Software Systems 2               | 5   |

|               | 4.1                    | Verifying Abstract Designs                         | :5  |

|               | 4.2                    | Verifying Implementations                          | 6   |

|               |                        |                                                    |     |

| 5             | Sun                    | nmary 2                                            |     |

|               | 5.1                    | A Unification Algorithm for Computing Successors 2 | 9   |

|               |                        | Background                                         | 9   |

|               |                        | Related Work                                       | 0   |

|               |                        | A Description of the Algorithm                     | 1   |

|               |                        | Contributions                                      |     |

|               | 5.2                    | Modular Reachability Analyser                      |     |

|               | 9.2                    | Background                                         |     |

|               |                        | Related Work                                       |     |

|               |                        |                                                    | , , |

|    |                     | Contributions                                                                 | 34                         |

|----|---------------------|-------------------------------------------------------------------------------|----------------------------|

|    | 5.3                 | Parallelised State Space Enumeration                                          | 34                         |

|    |                     | Background                                                                    | 35                         |

|    |                     | Related Work                                                                  | 35                         |

|    |                     | Contributions                                                                 | 36                         |

|    | 5.4                 | Modular State Space Enumeration                                               | 37                         |

|    |                     | Background                                                                    |                            |

|    |                     | Related Work                                                                  |                            |

|    |                     | A Description of the Algorithm                                                |                            |

|    |                     | Contributions                                                                 |                            |

|    | 5.5                 | Managing Component-Oriented Enterprise Applications                           |                            |

|    |                     | Background                                                                    |                            |

|    |                     | Related Work                                                                  |                            |

|    |                     | Contributions                                                                 | 41                         |

| 6  | Con                 | clusion                                                                       | 43                         |

|    | 6.1                 | Topics for Further Research                                                   | 43                         |

|    |                     |                                                                               |                            |

| Re | efere               | nces                                                                          | 45                         |

|    |                     | nces rections to Publications                                                 | 45<br>60                   |

|    | Cor                 |                                                                               | 60                         |

| A  | Cor                 | rections to Publications                                                      | 60<br>61                   |

| A  | Cor                 | rections to Publications orithm Listings                                      | <b>60 61</b> 61            |

| A  | Cor<br>Alge<br>B.1  | rections to Publications  orithm Listings  Sequential State Space Enumeration | 60<br>61<br>61<br>61       |

| A  | <b>Algo</b> B.1 B.2 | rections to Publications  orithm Listings  Sequential State Space Enumeration | 60<br>61<br>61<br>61<br>62 |

### **PREFACE**

This dissertation is the result of studies and research at the Laboratory for Theoretical Computer Science of Helsinki University of Technology from 1998 to 2003. I am grateful to my supervisor Doc. Nisse Husberg, to Prof. Emeritus Leo Ojala and to Prof. Ilkka Niemelä, the current head of the laboratory, for providing me with an opportunity to work at the laboratory, and to my colleagues, especially Dr. Kimmo Varpaaniemi and Dr. Keijo Heljanko, for valuable feedback and discussions.

The work was funded by the Helsinki Graduate School on Computer Science and Engineering, the National Technology Agency of Finland (TEKES), the Nokia Corporation, Elisa Communications, the Finnish Rail Administration, EKE Electronics, Genera, the Academy of Finland (Project 47754) and by personal grants from Tekniikan Edistämissäätiö and Jenny and Antti Wihuri Fund. Without the funding and grants of these organisations, full-time studies and international visits would not have been possible.

Last but not least, I would like to thank my wife Heli and my friends and family for support and encouragement.

Otaniemi, 24<sup>th</sup> of October, 2003

Marko Mäkelä

#### **List of Publications**

- [P1] M. Mäkelä. Optimising enabling tests and unfoldings of algebraic system nets. In José-Manuel Colom and Maciej Koutny, editors, Application and Theory of Petri Nets 2001, 22<sup>nd</sup> International Conference, ICATPN 2001, Newcastle upon Tyne, England, June 2001, Lecture Notes in Computer Science 2075, pages 283–302, Springer-Verlag, Berlin, Germany.

- [P2] M. Mäkelä. MARIA: Modular reachability analyser for algebraic system nets. In Javier Esparza and Charles Lakos, editors, Application and Theory of Petri Nets 2002, 23<sup>rd</sup> International Conference, ICATPN 2002, Adelaide, Australia, June 2002, Lecture Notes in Computer Science 2360, pages 434–444, Springer-Verlag, Berlin, Germany.

- [P3] M. Mäkelä. Efficiently verifying safety properties with idle office computers. In Charles Lakos, Robert Esser, Lars M. Kristensen and Jonathan Billington, editors, Formal Methods in Software Engineering and Defence Systems 2002, Adelaide, Australia, June 2002, Conferences in Research and Practice in Information Technology 12, pages 11–16, Australian Computer Society Inc.

- [P4] M. Mäkelä. Model checking safety properties in modular high-level nets. In Wil M.P. van der Aalst and Eike Best, editors, Application and Theory of Petri Nets 2003, 24<sup>th</sup> International Conference, ICATPN 2003, Eindhoven, The Netherlands, June 2003, Lecture Notes in Computer Science 2679, pages 201–220, Springer-Verlag, Berlin, Germany.

- [P5] J. Järvenpää and M. Mäkelä. Towards automated checking of component-oriented enterprise applications. In Daniel Moldt, editor, Second Workshop on Modelling of Objects, Components and Agents, DAIMI report PB-561, pages 67–85. University of Århus, Denmark, August 2002.

The dissertation consists of the five publications listed above, and a dissertation summary. Publications [P1]–[P4] cover state space analysis methods, and they have been solely written by the current author.

The publication [P5] is joint work with Jukka Järvenpää, who came up with the idea of applying state space analysis to component-based software and business logic. The formal modelling principles and the experiment presented in [P5] were written by the current author, while Mr. Järvenpää covered more practical aspects, such as the prototype front-end for the Maria tool, to be used in simulated application maintenance work.

#### 1 INTRODUCTION

Until late 1980's, home and office computers used to be isolated systems that performed one task at a time. It was fairly easy to avoid and to correct programming errors, since the software was programmed to interact with at most one entity at a time—if the printer or the disk drive was slow, the user would have to wait for his turn.

Today, microprocessors or microcontrollers are replacing mechanical or electric control systems, and they have enabled entirely new application areas, such as mobile telecommunications. The computing nodes are networked with each other, and the software they execute responds to events arriving from independent sources, such as sensors, user interfaces, or other computing nodes.

Clearly, an asynchronously operating distributed system is more difficult to manage than an isolated appliance that performs one task at a time. On the other hand, a fault in an isolated system has negligible consequences when compared to a design flaw that may lock up a telecommunication network, allow trains to collide in a railway safety system, or discriminate some users in a congested situation.

Ensuring the correct operation of distributed software systems is a challenge. Due to the nondeterministic nature of asynchronous systems, it may be hard to reproduce faults. A timing-related error might not show up at all when the software has been compiled with support for debugging enabled, or when it is executed in a debugger. Computer aided verification has been suggested as a supplementary method to testing and code reviews. The idea behind it is to utilise the increasing computing capacity to ease the design of complex systems.

One of the most promising computer aided verification methods is model checking [33]. The basic idea is to construct a graph that contains the reachable states of the system (or a model of it) as its nodes and the state transitions as its edges. This graph is known as the Kripke structure of the system, if its nodes are labelled with atomic propositions that characterise the state of the system. The property we would like to verify can be specified in temporal logic [33, Chapter 3]. A model checking algorithm can determine whether the Kripke structure is a model of the logic formula, i.e., whether the system meets its specification, and reproduce execution traces that demonstrate detected violations.

Two decades ago, when model checking tools could handle up to tens of thousands of states, the method was considered impractical by some researchers [159]. Even though computers have evolved since then, there still is a practical problem: almost any system of interest has a huge number of reachable states. If the size of the system is characterised with a parameter, such as the number of processes or the capacity of message channels, the number of reachable states tends to grow exponentially in this parameter [150, Section 1]. Symbolic model checking [117] tries to solve the problem by representing sets of states with formulae. It has been successful in the verification of hardware designs, which use simple data types and operations. Alas, it is less likely to achieve similar reductions in software specifications whose logical structures are less regular [25].

1 INTRODUCTION 3

In explicit state space enumeration, each node in the state graph is visited (and often stored) separately. This can require huge amounts of memory and processing time. The state explosion problem can be countered by applying reduction methods, which ignore some states that do not affect the property being checked, or by simplifying the model.

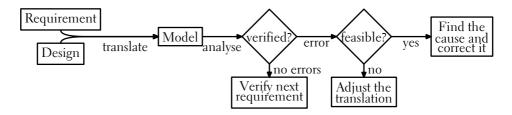

Abstract (simplified) models can be constructed at early stages of development, allowing principal design problems to be detected and corrected before any implementation work is started. Provided that the model reflects the software architecture and the modelling formalism supports the concepts of the implementation language, it is possible to keep the model up to date, in order to verify new features added to the implementation. However, it can be expensive and error-prone to maintain the model by hand. If the software architecture facilitates an automated translation from code to abstract models, model checking can reveal an order of magnitude more errors than testing [75].

Unfortunately, model checking is not yet a widespread technique in software engineering. This could be attributed to the lack of efficient computer tool support. Tools designed for interactive use may have problems with large automatically generated models due to inefficient use of memory. On the other hand, heavy-duty model checking tools may lack a simulator, which can be frustrating to someone who would like to experiment with a model without having any specific verification question in mind. Also, the formalism supported by the tool could be inefficient in certain tasks. For instance, modelling point-to-multipoint communications in a language based on processes communicating over point-to-point links can generate unnecessary overhead both in the model and its state space. A generic high-level formalism, such as the algebraic system nets [98] implemented in the MARIA tool [P2], allows a broad range of systems to be modelled in a compact and comprehensible way.

This research focuses on efficient techniques for modelling and model checking parallel and distributed high-level software systems.

#### 1.1 Interfaces and Abstraction in Software Systems

The complexity of software systems can be managed by partitioning designs into layers containing replaceable modules that provide services. A classic example is the reference model for open systems interconnection [84], the "protocol stack" where each layer provides refined service to upper layers by making use of services provided by lower layers. The lowest layer is the physical communication medium, and the highest layer is the distributed application that provides service to real-world users.

Layers are inherent in many operating systems, programming languages and programming frameworks. Programming frameworks implement high-level interfaces to the system resources. The resources may be managed in pools in order to optimise performance or to provide automatic deallocation, so that the application code can be kept simpler.

The layers and service interfaces provide a nice form of *abstraction*. The same application program module can be executed in any environment that provides the required interfaces. When a system has been

built of suitably isolated parts, one can reason about its modules without knowing the complete system in detail.

For instance, the designer of an Internet-based "shopping cart" application can assume that all underlying hardware and software components work properly. The components could include the TCP/IP stack [81] implemented in the participating devices, a database management system, and library routines for authenticating users and tracking sessions. To ensure the correct operation of the whole system, the designer can focus on the high-level application logic, as discussed in [P5].

At execution time, distributed or parallel software systems are partitioned into execution contexts called *processes* or *threads*, each of which represents a single flow of control. The processes can communicate with each other by passing messages or accessing shared memory areas. Depending on the application, the processes can perform a large number of internal computation steps between acts of communication. Distinguishing local actions from synchronising or communicating ones can lead to exponential savings [P4].

## 1.2 Objective and Methods

The aim of the research was to develop efficient computerised tools and methods for modelling and verifying parallel and distributed high-level software systems. Two places for improvement were identified:

- 1. The modelling formalism of a model checking tool should support the high-level concepts and operations of programming languages to avoid complicated or inefficient translations that are tedious and error-prone to carry out by hand or to implement in a compiler.

- 2. Semi-automated means of deriving abstractions could enable the use of model checking tools on more complex systems, even if little or no model checking expertise is available.

The workload of model checking experts can be minimised by developing translators from engineering documents and program code to verification models and formal requirements. The closer the modelling formalism is to the programming language, the simpler the translator can be made. In the extreme case, no translator is needed—the software can be verified by executing it in a special environment, as in [23].

There are multiple levels of abstractions. High-level programming languages hide many details, such as memory management, processor register allocation and instruction scheduling. Abstract data types hide the details of data structures. If the modelling tool directly supports the abstract concepts, systems that make use of them can be modelled more compactly and explored more efficiently than with a lower-level tool.

On a higher level, abstraction is provided by layered or modular software architectures. If there exist abstract descriptions of the components, the system can be inspected one component at a time, replacing the rest with abstract models. If not, modular state space exploration can create abstractions "on-the-fly" by exploring the components in isolation and considering only those global states where interactions occur.

1 INTRODUCTION 5

A constructive research method was applied. The algorithmic ideas for efficient state space enumeration of high-level models were implemented in the tool Maria, which was designed from the scratch by the current author. The ideas were presented and implemented for high-level Petri nets, but with the exception of [P1], it is straightforward to adapt them to other formalisms.

#### 1.3 Contributions

This dissertation presents algorithms and methods that make the software reliability verification process more efficient. Publications [P1, P3] describe efficient algorithms for exploring large state spaces of high-level models. Publication [P2] shows how the usability of a model checking tool can be improved by combining interpreter and compiler techniques. Publications [P4, P5] present two methods for alleviating the state space explosion [150] of modular or component-based systems.

The main contributions of each of the publications are the following:

- [P1] One of the most time-consuming tasks of state space enumeration tools for high-level Petri nets, determining the assignments under which transitions are enabled, is viewed as a unification problem. The presented algorithm, boosted with a pre-processing step for reordering the input, has been optimised for computing successor states while constructing the assignments. A variation of the algorithm is demonstrated to produce significantly smaller unfolded place/transition systems for certain instances of high-level nets than the canonical method [98, Section 4.1].

- [P2] A freely available, extensible state space enumeration tool for a class of high-level Petri nets is presented. Unlike [10, 155], the tool has been designed for checking automatically translated models of software written in high-level languages. The interpreter-driven mode of operation makes it easy to simulate large models, while compiled code speeds up exhaustive analysis tasks.

- [P3] The distributed version of the state space enumeration algorithm in Maria [P2] is presented. The algorithm is not designed for a dedicated computing cluster like [21, 69, 76, 82, 115, 124, 146], nor is it tightly coupled with any formalism like [26, 124, 137], but it is optimised for utilising the idle processing time of ordinary office computers. The central server simplifies management, allows dynamic load balancing and reduces the memory consumption at the computing nodes. Experiments made with up to twelve clients show over 90 % processor utilisation, depending on the average branching degree of the model, and the utilisation factor has been demonstrated to improve when state space reduction methods are applied.

<sup>&</sup>lt;sup>1</sup>Translators for PROD [155] have problems with data types [78] or restrict the source language [17, Section 3]. The developers of a translator from SDL [89] into Design/CPN [119] suggest the development of a new model checker as future work [30, Section 8].

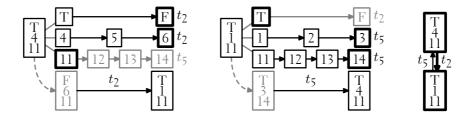

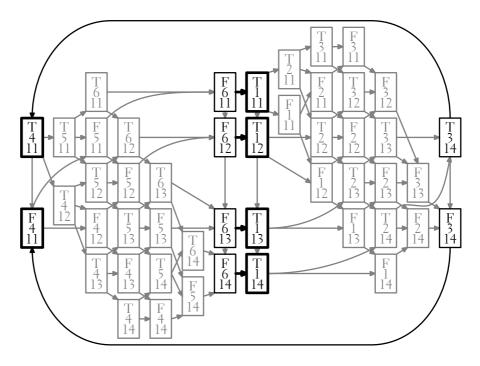

- [P4] A simple algorithm is presented that checks safety properties in systems consisting of loosely coupled modules. Instead of generating a single state space of all possible interleaved executions of the modules, the algorithm constructs local state spaces for each module and only includes the synchronisation actions in the combined state space, which can greatly reduce the processing power requirements. The work is based on an earlier proposal [28], but the presented algorithm supports nested modules, uses simpler data structures and has been implemented—in a way compatible with [P3].

- [P5] A method of modelling and model checking data-centric enterprise applications built on component-based frameworks is presented. The systems are formalised by combining automatically derived models of the high-level application logic with previously stored models of component behaviour. Related work has been reported on telephone switches [75, 76] and device drivers [112].

The Structure of the Dissertation The dissertation consists of five publications and this dissertation summary, structured as follows.

Section 2 is an introduction to verification. It compares the available formalisms and techniques for verifying the correct operation of parallel and distributed systems. Section 3 presents state space enumeration, the general-purpose technique for model checking high-level systems, and describes options that allow more complex systems to be explored. It provides the background information needed for understanding the three algorithms [P1, P3, P4] that have been implemented in the MARIA tool [P2]. Section 4 describes the workflow of verification and estimates the degree of automation that can be achieved with the use of different tools and methods. Finally, the publications are summarised in Section 5 and our conclusions and outline for future development are presented in Section 6.

1 INTRODUCTION

7

#### 2 VERIFICATION

Jörg Desel [43] defines three terms for determining the quality of a system, or a model thereof: validation, verification and evaluation. Validation answers the question "was the right system built?" by determining whether the system fulfills its intended purpose. Verification answers the question "was the system built right?" by proving that the system matches its specification. Evaluation captures other aspects of the system, such as usability and end user acceptance, maybe performance as well.

This section concentrates on verification, determining whether a system matches its requirements. Furthermore, it concentrates on nondeterministic systems, which are difficult to inspect by testing, as variations in timing can make them behave differently on the same input. To automate verification, both the system and the requirements must be formalised. Logic seems a natural choice for formulating requirements. For modelling computing systems, there are many *formalisms*, which differ in their preferred *level of abstraction*.

In top-down design methodologies, the system is first described at an abstract level. The abstract description is divided into components or modules that are gradually refined towards concrete implementations. Kurshan [102, Section 8.6] discusses the concept of stepwise refinement:

[T]here is a circle of thinking which supports the view that one may start with a high-level (abstract) specification, refine it in a linear fashion down to a model which may be physically implemented (adding more detail at each step) and be done. It is thought that if each model is consistent with its more abstract specification (in the refinement succession), then one knows that the lowest-level model is true to each of its specifications.

High-level (abstract) models can also be thought as "rapid prototypes" that permit early "debugging." The top-down methodology is well suited for proof systems, such as the Temporal Logic of Actions [105]. According to Lamport [105, Section 9.5.1], the refinement steps could even be automated to some degree:

Derivation of a program by a rigorous procedure that guarantees its correctness is preferable to post hoc verification. [...] Any method for proving that one program implements another can be used as the basis for program derivation. [...] Unfortunately, we know of no concurrent algorithm used in a real system that was systematically derived, not simply justified by post hoc verification.

In bottom-up design methodologies, the "low level" entities are defined first and used as building blocks of more and more complex entities. The "low level" entities can be readily available as the primitives of a programming language or the services of the operating system or existing software packages. They can also be constructed by the designer.

Many programmers have a pragmatic approach to problems. They construct small prototypes and experiment with them in order to become familiar with the problem at hand. The question is whether the produced code meets its requirements. In the ideal world, there would exist formal requirements and descriptions of each module. In practice, no detailed requirements might be available, and everyone working on the system could have a slightly different view. However, every system should fulfill some generic safety properties, such as the absence of deadlocks, failed assertions, arithmetic errors, data integrity violations or resource leakages. Such properties can be verified by model checking or state space enumeration, which is the topic of Section 3.

## 2.1 Formulating and Checking the Desired Properties

Dwyer et al. [49] motivate *specification patterns*—a high-level front-end to temporal logics—with the following example:

For example, consider the following requirement for an elevator: Between the time an elevator is called at a floor and the time it opens its door at that floor, the elevator can arrive at that floor at most twice. To verify this property with a linear temporal logic (LTL) model checker, a developer would have to translate this informal requirement into the following LTL formula:

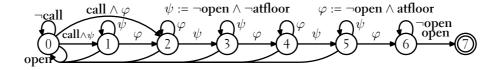

In the automata-theoretic approach to verification, a desired property of a system is negated and translated into an automaton. Figure 1 illustrates such an automaton for our property. The leftmost state is the only initial state, and the rightmost one is an accepting, or a "bad" state. Also the state space of the model is interpreted as an automaton. A synchronised product automaton of the two automata is constructed. The system is in error if a "bad" state is reachable in the product. State space analysis tools look for such states and produce error traces—executions from an initial state of the two automata that lead to an error.

The automaton in Figure 1 contains only one "bad" state. The shortest path to this state is via the edge labelled  $call \land \neg open \land atfloor$  followed

Figure 1: An automaton for the property that an elevator called at a floor may arrive at the floor at most twice without opening its door.

2 VERIFICATION 9

by horizontal edges. Informally, the first step—from state 0 to state 2 of the automaton—corresponds to the case where the elevator has already arrived at the floor when it is called. Then, keeping its door shut, the elevator leaves and arrives twice. After that, in state 6 of the property automaton, it does not matter how many more times the elevator might arrive. An error is signalled once the elevator door finally opens.

Does an elevator whose door never opens fulfill this property? Intuitively, one could believe "no," but the "bad" state in Figure 1 cannot be reached without the door being open at some point. This example shows that the desired properties have to be formulated carefully, and even the obvious requirements must be stated explicitly—computers are dumb.

We believe that a substantial amount of errors can be captured with assertions or invariants, stating that some condition must hold in each possible state of the system or whenever a given program statement is about to be executed. Such properties can be directly checked in the state space of the model—without computing a product automaton—since the property automaton has only one non-accepting, or "good" state.

Many properties can be automatically derived from engineering documents, such as the referential integrity rules for databases, or assertion statements in source code. Assertion statements of the form  $\mathbf{assert}(q)$  can be formulated in linear temporal logic as  $\Box(p \to q)$ , where p indicates the point of execution. In MARIA, these can be translated into **reject** statements or intentional evaluation errors [**P3**, Section 2.1].

Havelund and Skakkebæk [66, Section 2.1] and Holzmann [75, Section 6] propose temporal assertion statements, such as **assert\_eventually**(q) for  $\Box(p \to \Diamond q)$ . As opposed to *safety* properties, these *liveness* properties require something to *eventually* happen, without setting any fixed bound. An automaton on infinite sequences is needed for expressing liveness. The liveness model checker [106, 107] in our toolset has been built on top of the safety model checker [**P3**].

## 2.2 Modelling Formalisms

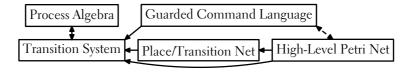

Before a system can be verified, a model of it must be constructed using some formalism. Figure 2 shows the relations between some families of modelling formalisms. State spaces consist of the reachable states of a system and transitions leading from a state to another. They can be presented with transition systems or process algebra. Higher-level models can be expanded to transition systems, and high-level Petri nets can be unfolded to place/transition nets. There exist translations between some guarded command languages and Petri nets. There is some variation in each family. For instance, transition systems can be defined to include

Figure 2: Some language families for describing computations.

state propositions [151], or the emphasis may be on the transitions or actions, as it often is in process algebra and in compositional modelling.

In software engineering, one use of models is to convey information in a more structured format than natural language, as in UML class diagrams [125, Part 5] or sequence diagrams [125, Part 7]. Often such models do not specify all details, or they lack exact semantics. For verification purposes, a computer must be able to interpret all of the model.

Timing can play a significant role especially in real-time systems. In untimed formalisms, the actions or transitions are not assigned any durations or timing constraints. Only the order in which events occur is observable—nothing exact can be deduced about the time. In timed formalisms, enabled transitions may be forced to occur within a predetermined time, and they may be assigned a probability for occurring.

This section presents some of the modelling formalisms that are supported by computerised verification tools. Emphasis is on untimed formalisms, since certain types of timed transitions can be simulated by quantising the time in discrete ticks, as in [20].

#### **Guarded Command Languages**

Guarded commands play a central role in Dijkstra's mini-language [45, Chapter 4]. A guarded command is defined as a sequence of statements that may be executed if a Boolean expression holds. The predicates of programs expressed in the mini-language are solely transformed by assignment statements. The only other statements are the repetition (do...od) and the choice (if...fi) of guarded command sets.

Dijkstra's original work is directed towards the development of sequential programs. Extensions for describing parallel systems include **parbegin...parend** blocks [44] and message passing [71].

One of the best known model checkers for communication protocols, SPIN [74] of Bell Labs, is based on a process oriented guarded command language where processes may communicate via message channels.

Dijkstra's notation has also influenced Mur $\varphi$  [46], SMV [117] and the Basic Petri Net Programming Notation of PEP [13, Section 3.1].

## Process Algebra

In the Calculus of Communicating Systems [120, 121] (CCS), the processes may have *internal actions* denoted by the  $\tau$  symbol, and a pair of processes can engage in a synchronisation event where one process "sends" and the other "receives" a symbol, e.g.,  $\alpha$  and  $\bar{\alpha}$ . The Algebra of Communicating Shared Resources [32] extends CCS by allowing prioritised actions that may consume resources and time.

In 1978, Hoare introduced the Communicating Sequential Processes (CSP) using a guarded command language notation [71] inspired by Dijkstra [45, Chapter 4]. In this definition, processes communicated in a similar fashion to CCS, by sending and receiving messages via synchronised point-to-point channels. In 1985, Hoare defined CSP in the form it is known today in his famous book [72]. In [72, Section 7.4.1], he compares CCS and CSP. The major semantic difference is that CSP allows any number of processes to take part in a synchronisation.

2 VERIFICATION 11

The term "process algebra" does not only refer to algebraic notation for transition systems, but also to a method of verifying concurrent systems. Process algebra offers an alternative to model checking (Section 2.1): The model of the system can be shown to be equivalent with a simpler model where the property obviously holds.

## **Transition Systems**

Transition systems are perhaps the simplest way of describing the behaviour of a computing system. As in Figure 1, they can be viewed as directed graphs of the possible state transitions of a system. They can also be represented textually in some process algebraic notation.

Transition system tools include Cæsar/Aldébaran [52] and the recently published Tampere Verification Tool [151] (TVT). User-definable rules for parallel composition allow TVT to serve as a verification backend for many process algebras, including LOTOS [85], which is also supported by Cæsar/Aldébaran. LOTOS features data types, variables and parameterised actions, and various synchronisations.

Transition systems are a simple formalism. To model complex behaviour, it may be practical to construct a higher-level model and translate the states spaces of its components into transition systems. Transition systems can be generated from Petri net models with MARIA [P2], and from other high-level specifications, such as an SDL [89] specification of a communication protocol [110].

Transition systems can be reduced or compared with respect to various equivalence relations, such as strong bisimulation [121, Definition 7.1.1]. This is useful when the system is modelled as a parallel composition of components. The composition can be made smaller if it is constructed incrementally, hiding actions and reducing the resulting intermediate systems whenever possible. Kaivola [93] presents efficient reduction and comparison algorithms for the NDFD equivalence relation [93, Definition 4.2.7], which preserves all properties expressed in the next time-less linear temporal logic [93, Section 3.2].

Transition systems can also be viewed as a simple formalism for describing state space reduction techniques. It is not necessary to explicitly construct transition systems in order to apply the techniques. Instead, the techniques can be directly implemented in state space enumeration tools, like the partial order reduction methods in SPIN [74, Section 3.3] and PROD [155] and the modular state space exploration in MARIA [P4].

#### Petri Nets

Computing systems consisting of multiple processing units usually communicate via shared variables (common storage that can be read or written by multiple processing units) or by exchanging messages over point-to-point or point-to-multipoint communication channels. In transition systems and process algebra, modelling shared storage easily requires large numbers of actions. Guarded command languages have a provision for shared data, but their message primitives are usually limited to point-to-point channels. It would be nice to have a more generic formalism that supports both shared data and arbitrary synchronisations.

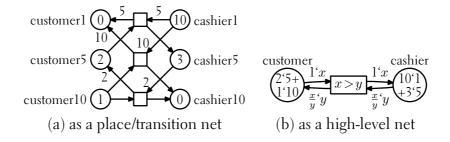

Figure 3: An algorithm for breaking money.

In 1962, the dissertation of Carl Adam Petri, Kommunikation mit Automaten, introduced a graphical formalism for modelling synchronisations and communications between automata. The draft standard [15] defines two classes of Petri nets: place/transition nets and high-level nets.

Place/transition nets [15, Clause 10.1] have places that contain a non-negative amount of tokens, which can be removed or added by the occurrences of transitions. A transition is connected to places via input arcs and output arcs whose weights indicate how many tokens the occurrence of the transition removes from the input places and adds to the output places. A transition is enabled (it may occur) if its each input place contains at least as many tokens as the weight of the arc indicates. The state (marking) is defined as the number of tokens in each place.

Let us consider a situation that could happen near a coin-operated machine. A customer comes to a cashier with a bank bill in his hand, asking "Could you break this for me?" The cashier then changes the money to an equivalent amount of money in smaller coins or bills. In Figure 3(a), the money owned by the two parties is represented by the marking of six places, denoted with circles. The marking is represented with numbers enclosed in the place symbols. In Figure 3(a), the customer has two coins or bills of value 5 and one of value 10.

The possible actions are modelled by transitions, drawn as rectangles. The input and output arcs are denoted by arrows leading to or from the transition symbols. Arcs are associated with positive integer weights. By convention, weights of 1 are omitted from diagrams. In our algorithm, the cashier always returns one type of money, e.g., ten small coins for one big bill, as in the transition in the center of Figure 3(a).

In high-level Petri nets [15, Clause 10.2], places and tokens are associated with data types (also known as colours or algebraic sorts). In other words, the tokens can represent data that is stored in the places. Figure 3(b) is a more compact version of Figure 3(a). The six places are folded to two places whose markings are multi-sets of coin or bill denominations. The rule for breaking money can now be specified with one transition that has two variables: x for the money offered by the customer and y for the change given by the cashier. These variables are constrained by the transition guard x > y. The available denominations are no longer hard-coded in the model, as in Figure 3(a).<sup>2</sup>

2 VERIFICATION 13

<sup>&</sup>lt;sup>2</sup>To allow arbitrary positive integers as denominations, the guard must be refined so that x/y is an integer, since the cashier cannot return fractions of coins or bills.

High-level nets are better suited for detailed modelling of high-level software systems than place/transition nets, since the arithmetic operations in the software can be directly translated into arc inscriptions and transition guards. If the data domains of a high-level net are small enough, the net can be *unfolded* to a place/transition net of manageable size. Figure 3(a) depicts the unfolded counterpart of Figure 3(b).

Less expressive power often means more analysis power. Structural analysis makes it possible to prove certain types of properties for a large class of systems. Structural properties are much easier to derive for place/transition nets than for high-level nets. The structural properties of a place/transition net simply depend on its topological structure [123, Section VII].

The computer tools for analysing Petri net models range from research prototypes to commercial packages. PEP [13] and LoLA [136] operate on ordinary place/transition systems. They can analyse simple high-level net models via unfolding. Tools that operate directly on high-level nets include Prod [155] (which is based on predicate/transition nets [59]), Design/CPN [119] and CPN/Tools [10] (which support coloured nets [91]) and Maria [P2] (for algebraic system nets [98]).

Originally, Petri nets were an untimed formalism. Extensions have been developed for performance modelling and analysis [123, Section IX]. Analysis tools include GreatSPN [27] for timed and stochastic Petri nets and SMART [31] for various stochastic modelling formalisms.

Petri nets may have a shortcoming when it comes to modelling complex software systems: they lack structuring capabilities. From the theoretical perspective, all transitions are equal, and the data and control flows are indistinguishable from each other. It may be easier to understand and maintain nets when they are divided into fairly isolated components or modules. In the Design/CPN editor, the net can be drawn on multiple pages, which are connected via shared places or substitution transitions—a special form of macro expansion. The textual modelling language of MARIA supports similar techniques. MARIA can preserve some structure during analysis, as it supports modular exploration of multiple nets that are synchronised via shared transitions [P4].

For modelling object-oriented software systems, more sophisticated structuring capabilities have been proposed. Proposed extensions include Object Petri Nets [103], Concurrent Object-Oriented Petri Nets [14] and Agent-Oriented Coloured Petri Nets [122] that have evolved into Reference Nets [101]. One reason why the tool support on these formalisms is directed toward modelling, simulation and executable code generation rather than verification is the large number of combinations in which identifiers can be assigned to resources or objects. Each object is assigned an abstract value that uniquely identifies it throughout its lifetime. If the pool of available identifier values is limited to n, at most n objects can coexist. For instance, the identifiers for objects representing the items of an n-element linked list can be chosen in  $n! = n(n-1) \cdots 3 \cdot 2 \cdot 1$  ways from such a pool. That is, there are n! equivalent combinations that are considered distinct. Techniques that address this problem are discussed in Section 3.2.

#### Logic

One of the most abstract modelling formalisms is logic. There, the possible states of a system are specified with a number of propositions or conditions. Verifying a property of the system is a matter of checking whether the formula stating the property can be derived from the formulae that describe the system by applying some proof rules.

Chandy and Misra [24] presented an abstract way of developing algorithms. Their Unity notation has no explicit control flow. Mapping Unity algorithms to hardware architectures is nontrivial, as the implementations of an abstract algorithm on shared or distributed memory can heavily differ from each other. Also Reisig [132] describes abstract distributed algorithms, using algebraic nets. Like Chandy and Misra, he presents a system for proving safety and a limited form of liveness.

The Z notation has recently become an international standard [87]. Several computerised type checkers and theorem proving tools are available. Z is related to B [3] and VDM [68, 88], which is closely related to Meta IV, a language for defining semantics. Extensions to Z include objects and CSP-style parallel composition [53].

Lamport's Temporal Logic of Actions [105] (TLA) is an untyped language based on linear temporal logic and a set of axioms and proof rules. The behaviour of the system is described with mathematical and logical equations—there is no concept of assignment. TLA is intended to be a tool for specifying concurrent algorithms at a very abstract level and proving that they satisfy the desired safety and liveness properties.

## 2.3 Specialised Verification Methods and Tools

There exist several methods and computerised tools for verifying formal specifications. Some are specialised in certain types of systems, while state space enumeration can be adapted for any kind of a finite system. The specialised techniques usually support a restricted set of built-in operations, and they can often manage very large or infinite state spaces.

If there exists a specialised technique for analysing a particular type of a system, it usually makes sense to use that technique. There are two possible problems. Sometimes, it may be difficult to translate the system description into the formalism used by the tool. If the tool makes use of computationally complex heuristic algorithms, it may exhaust the available computing resources even when checking a fairly simple model.

The remainder of this section presents some specialised verification methods and discusses their suitability for verifying software systems. Of these methods, symbolic model checking is closest to the generic technique of state space enumeration, which is covered in Section 3.

#### **Theorem Proving**

The strength of theorems is that they can assert that something works for a large or infinite number of parameter combinations. Proof systems are efficient for verifying systems consisting of little control logic, such as special-purpose arithmetic units, as in [16, Chapter 3]. Theorem proving also suits well for abstract specifications, like those written in DisCo [90],

2 VERIFICATION 15

a specification language for reactive systems that is based on TLA [105].

If the system uses complex data structures or if its control logic consists of many computing steps—as the case often is with software—the logic formulae may become too complex for any theorem proving system. Due to the heuristic nature of theorem proving algorithms, most theorem provers require quite a bit of manual intervention. A small modification to the model can confuse the heuristics and lead the algorithm to an infinite loop.

If the property being verified does not hold, the theorem prover might not be able to clearly show what is going wrong. The problem can be diagnosed or the proof validated with an interactive animator or simulator, as in the DisCo tool set [96, Section 4], or with a model checker, as in the Symbolic Analysis Laboratory [12] (SAL).

Both DisCo and SAL delegate theorem proving to the Prototype Verification System [126] (PVS). Another theorem prover for typed higher-order logic (and the Z notation) is ProofPower [5], which is based on the extensible language Standard ML. MAUDE, a framework for building theorem provers, is a tool for rewriting logic with user-defined strategies. It can be used as a model checker or simulator [34, Section 8.1].

#### **Rewriting Systems and Equivalence Tests**

Most tools for process algebra or transition systems include some kind of a rewriting system for reducing or comparing models with respect to some equivalence relation that preserves the property being verified. VERSA [32] rewrites process algebraic models and tests transition systems for equivalence.

When the system is designed in a top-down fashion, equivalence tests can be used for verifying each refinement step, proving that the system implements its specification. However, the refinement steps in software system development are rarely presented in formal notation.

Since process algebras are action-oriented, it may be difficult to efficiently translate data-intensive software systems into them. Simply instantiating distinct "read" and "write" actions for each possible value of each variable could make the model too large to be processed in any tool.

#### Structural Analysis

Certain properties of a system can be checked without considering its dynamic behaviour. For instance, modern compilers for strongly typed high-level programming languages ensure that the data types are used in a consistent way. They may also warn about variables or procedures that have been defined but are never used.

Advanced compilers even issue warnings for procedure-local variables that *may* be used before they are initialised. In the general case, the variable can be referred to in conditional blocks, and the conditions can be affected by the environment of the procedure. Thus, the structural analysis performed by the compiler cannot be affirmative in all cases.

Some properties or analysis algorithms may apply to certain classes of models. With structural analysis, a model can be determined to belong to a particular class. Then all properties proven for that class will trivially hold in the model, and there might be a more efficient analysis method. For instance, Murata [123, Section VI] summarises the liveness, safeness and reachability criteria for different topological classes of place/transition nets. He then demonstrates some "short-cuts" for one special case, marked graphs [123, Section VII].

Place/transition nets can also be classified by their matrix representations [123, Section VIII]. From matrix equations, it is possible to derive net *invariants* that hold for all possible initial states of the system. Transition invariants indicate possible loops of the system, and place invariants can be used for reasoning about the possible states of the system.

We believe that structural analysis augments other verification techniques. In high-level software systems, a relatively simple static analysis tool can locate simple programming errors more efficiently than a full-blown theorem prover or model checker. However, static analysis generally cannot prove or disprove arbitrary properties of a system.

## Symbolic Model Checking

Symbolic model checking methods manipulate data structures that represent sets of reachable states of the model. The data structure can be interpreted as a characterising function that maps state variables to truth values. The set consists of those states that the function maps to "true."

The actions of the model being checked perform operations on state variables. Symbolic methods translate these operations into operations on the data structures representing the sets of states. Thus, the effect of an action in the model can be computed in all previously discovered states of the system simultaneously. Therefore, symbolic model checking can explore very large, even infinite state spaces in limited time.

However, it can be nontrivial to map the operations on single states to operations on sets of states. Therefore, many symbolic model checking tools are limited to rather low-level description formalisms.

**Decision Diagrams.** Boolean Decision Diagrams [18] (BDD), which represent Boolean functions as directed acyclic graphs, have been particularly successful in verifying hardware designs, where the data types and operations tend to be simpler and more regular than in software [25].

Software systems make use of integers, arrays, and other high-level data types. In order to apply BDDs on such systems, the data types have to be mapped into Booleans. An integer variable must be translated into multiple Boolean variables, and any operations on it, such as addition or multiplication, have to be expressed with Boolean operators. Such a translation could greatly increase the size of the model. Predicate abstraction [41] is more viable, since it describes the state of the system with predicates, which are modelled with Boolean variables.

Data Decision Diagrams [39] generalise BDDs to arbitrary data types. The operations on the data types are not hard-coded in the algorithm, as with BDDs [18, Section 4], but they have to be formalised as homomorphisms on DDDs [39, Section 1.3]. This method could prove efficient on software systems, if some essential data types and operations were formalised and packaged in an extensible tool.

2 VERIFICATION 17

Complete finite prefixes. An interesting type of symbolic model checking that resembles structural analysis is the unfolding of finite-state place/transition systems into complete finite prefixes that describe their dynamic behaviour [118]. A prefix can in some cases be exponentially smaller than the reachable state space of the system, which makes the prefixes interesting for verification purposes.

In order to apply net unfoldings on software systems modelled with high-level Petri nets, one would have to unfold the models into place/transition nets. In practice, this is often infeasible due to the complexity of the used data types. Recently, the technique has been extended to high-level nets [97]. Even though the use of place/transition nets can be avoided, the high-level nets should be constructed carefully. For example, if "read" operations atomically shift the contents of FIFO buffers, the resulting prefixes may become very large due to the number of distinct events, one for each possible buffer content.

Lossy FIFO systems. A distributed system that consists of processes communicating via unbounded channels can have an infinite number of reachable states. However, it is possible to prove safety properties of such systems with a backward reachability analysis algorithm [2].

If there is no abstract definition of the processes, it can be tedious to construct the state machines by hand. Leppänen and Luukkainen [110] extracted the state machines from a formal model of a communication protocol by partitioning the model and performing state space enumeration on the partitions.

A similar treatment could be given to program code, by repeatedly executing the code of each process for a bounded number of steps, simulating "receive" actions with nondeterministic choice of possible actions, as in the Verisoft tool [23]. However, this would generate finite trees of observed actions rather than nonterminating automata. Folding the trees into cyclic graphs may require a considerable degree of insight and manual work.

Bounded Model Checking. In bounded model checking, a non-terminating system is searched for counterexamples to a given property for a bounded number of execution steps. The technique can be implemented in symbolic model checking as well as explicit state space enumeration, and it can also be encoded as a propositional satisfiability problem, which can be solved by a tool like PROVER [141]. Amla et al. [4] compare these three approaches and conclude that BDDs perform best in deep counterexamples, while satisfiability solvers and random state space exploration are the winners for small bounds.

#### 3 STATE SPACE ENUMERATION

State space enumeration refers to techniques that incrementally construct the set of reachable states in a model by considering the effect of enabled actions in each reachable state separately. The basic technique can be applied to any computing system whose states can be stored, restored and compared.

Appendix B.1 contains the basic state space enumeration procedure. Its three most important parameters are the initial state  $s_0$  of the system, the state transformation rules successors, and a function error(s) that identifies erroneous states. We do not specify the details of the procedure reportError. It could display diagnostic information and abort the exploration, either unconditionally or based on some criteria, such as the severity of the error or the number of errors reported so far.

The search algorithm makes use of two data structures: the set of states it has explored, and a collection of states that are waiting to be processed. It must be possible to insert items into the set and to check if the set contains a given item. The collection must support insertion and removal of items, and emptiness check. If the collection is a queue, then the search proceeds *breadth first*, guaranteeing that a shortest path to an error is found first.

State space enumeration is a general-purpose tool with one practical limitation: the model being analysed must have a limited number of states and enabled actions. Otherwise checking all the reachable states one by one will consume too much time or memory. This limitation can be alleviated by the use of different state space reduction techniques.

The rest of this section discusses the benefits of state space enumeration, compares state space reduction techniques, and presents ways to reduce the execution time of state space enumeration.

#### 3.1 Benefits of State Space Enumeration

Easy implementation. Unlike the specialised methods discussed in Section 2.3, state space enumeration can treat the function for computing successor states as a "black box." Thus, there is no need to model the system in detail, provided that the nondeterminism in it can be controlled by the model checking testbed. For instance, to check whether a computerised player of a two-player board game can lose a game it starts, it is sufficient to have a program interface to the function that computes the next move on a given board. The initial state  $s_0$  would be the empty board, and the successor relation can be defined as the next move of the computerised player combined with all possible moves of its opponent, which would be simulated by our verification harness. The function error would identify those boards where the opponent has won.

Counterexamples. When there are millions of reachable states, merely providing the user with an erroneous state can be as frustrating as reporting "there is an error somewhere in your system." A *counterexample trace* is a sequence of actions that leads from the initial state to the error.

Unlike in proof systems, it is straightforward to construct error traces with the state space enumeration algorithm. Prod [155] extends the algorithm presented in Appendix B.1 by constructing a reachability graph that records the reachable states S as its nodes and the successor relation as its edges. When an erroneous state is found, a path to it can be found by graph traversal.

Not all edges of the graph need to be recorded in order to recover error traces. In fact, it is sufficient to maintain a mapping from each encountered state s' to its ancestor s, from which s' was first generated by successors. By repetitively applying this mapping, the trace can be obtained from the error to the initial state  $s_0$ . In order to conserve memory, Maria writes this mapping sequentially into a disk file [P3, Section 2.4], similar to  $\text{Mur}\varphi$ .

### 3.2 Alleviating the State Space Explosion

Almost any system of interest has a huge number of reachable states. If the size of the system is characterised with a parameter, such as the number of processes or the capacity of message channels, the number of reachable states tends to grow exponentially in this parameter [150, Section 1]. However, given a simple verification question, it is possible to throw some information away by creating a more abstract model or by applying some reduction in the state exploration algorithm, thus reducing the number of states that need to be explored [150, Section 4.1].

## **Eliminating Redundant Data**

One way of deriving abstract models is removing data and program code. Automated slicing techniques [147] can eliminate those parts that cannot affect the property being verified. A formal treatment of property preserving abstractions for process algebra and temporal logic has been given in [114]. The model can be reduced further if the behaviour of the system is over-approximated or under-approximated [66, Section 3.2]. However, errors found in an over-approximated model might not correspond to errors in the original system. Lazy abstraction [70], which applies predicate abstraction [41], starts with a very abstract model and refines it gradually to rule out errors that lack counterparts in the concrete model.

Models may contain redundant data. Kaivola [93] exploited the theory of data-independence [109] and showed that several properties of a communication protocol can be verified by considering only three distinct data packets that represent all packets circulating in the system. Valmari [150, Section 7.1] discusses the elimination of remnant variable values—that is, resetting variables whose current values will not be read. This technique has been implemented in Spin [74].

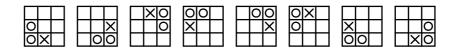

During state space exploration, it may be possible to identify some reachable states as redundant and ignore them. For instance, seven of the eight states shown in Figure 4 are redundant. Symmetry reduction techniques [83, 142] are essential in model checking certain types of systems, such as software systems that dynamically allocate resources. Juntila describes some approximative algorithms that can be applied to systems

Figure 4: The cells of an  $n \times n$  board can permuted in eight ways by rotation and reflection. The boards above look different but represent the same state. One of them could be chosen as a *canonical representative* of the group.

Figure 5: Concurrent execution of k independent processes consisting of n sequential actions produces  $k^n$  possible states (a). Atomic processes produce  $2^n$  states (b). Partial order reduction techniques reduce the number of choices in each state, and may thus explore only one path of kn states (c).

with a large number of dynamically allocated objects [92, Section 7].

#### **Dealing with Independent Actions**

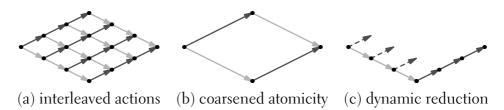

A key contributor to the state space explosion is nondeterminism caused by concurrently enabled independent actions. Figure 5 shows an extreme case and illustrates two examples of partial order reduction methods [128], which were originally presented as an aid for proving properties of parallel programs [6, 113]. The **atomic** keyword of SPIN [74] or a resource token [78] in Petri nets groups process-local actions into bigger indivisible steps. The result, in Figure 5(b), can be reduced further with path compression [**P3**, Section 4.1], which is a special case of a more generic method [95]. Both methods can be combined with partial order reduction, which ignores some enabled actions, as in Figure 5(c).

#### Compositional Verification

In compositional reachability analysis or modular verification [64, 160], the model is checked in multiple phases. It may be possible to transform the property being checked into something that can be checked on each component separately or on a composition of fewer components. Also, the full state space of the system can be composed incrementally, collapsing the sequences of internal actions in each intermediate composition.

When compositional verification is applied to labelled transition systems, as in [160] or [150, Section 7.3], the desired property is verified with respect to globally visible actions. For the purpose of verification, it may be necessary to make some internal actions visible and thus increase the size of the resulting composed transition systems. It is more efficient to decompose the automaton describing the property into something that can be directly synchronised with the components [25, Section 3.2].

One compositional technique that can be automated fairly easily is modular state space exploration, which is discussed in Section 5.4.

#### 3.3 Reducing the Memory Usage

A major problem of state space enumeration is its potentially large memory usage. In typical workstations, mechanical storage (disk space) is some orders of magnitude bigger and several orders of magnitude slower to access than solid-state memory (register file, caches and main memory). Therefore, it is essential for performance to reduce the size of the data structures, so that they fit in the main memory, or to design algorithms that reduce access to external storage, as in [130].

Two data structures that dominate the memory usage of the state space enumeration algorithm in Appendix B.1: the set S of reachable states and the "work queue" Q of states that have not been explored. The queue ensures that all states will be included in the search, and the set prevents infinite loops.

Many memory reduction techniques aim to reduce the number of states inserted into S, taking the risk that parts of the state space may be explored several times. Valmari [150, Section 5.4] presents an extreme case—a recursive algorithm that does not construct a set of reachable states but enumerates the set in each recursion level. He concludes:

[I]t is in theory possible to solve interesting verification tasks in relatively small memory. However, the known algorithms that do that consume unimaginable amounts of time.

## Relaxing the Loop Check

In the tic-tac-toe game, pieces are inserted to the board until one of the players wins or the board becomes full. Thus, no board state can occur twice in a game, and the set S that prevents infinite loops in the state space enumeration algorithm (Appendix B.1) can be omitted to save memory space.

Unfortunately, models of parallel and distributed systems tend to produce cyclic state space graphs. Therefore, the loop check can only be omitted in special cases, or states that are known not to recur can "bypass" the set S.

State Space Caching. The idea of state space caching [60, Section 2] is to discard parts of the set S when the exploration algorithm is running out of memory. Loops can be prevented by organising the unexplored states Q as a stack and by replacing the test  $s' \notin S$  with  $s' \notin S \land s' \notin Q$ . The drawback of this idea is that discarded states may be revisited if they can be reached via different execution paths. The situation can be ameliorated by applying partial order reductions and by adapting the cache deletion policy [60, Sections 4–5]. The compression of non-branching paths [P3, Section 4.1] bears some similarity with state space caching, but it also works in breadth-first search, producing short error traces.

The Sweep-Line Method. When the state space may contain cycles, some states must be stored in the set S, so that infinite loops can be

avoided. However, S could be reduced by removing those states that the system cannot possibly enter any more. For instance, the number of pieces on a chess board is a progress measure that never increases on any path consisting of valid moves. In the sweep-line method [99, 100], once all states with a given progress measure have been explored, they are discarded. The ability of MARIA to distinguish "visible" (transient) and "hidden" (persistent) states [P5, Section 4.3.3], called "predicate-bounded depth first search" in a later publication [50], is a special case of the generalised sweep-line method [100], which is compatible with non-monotonic progress measures. A practical problem with the sweep-line method is the definition of suitable progress measures.

#### **Compression Techniques**

Various compression techniques can be used for removing redundant information from the data structures S and Q used by the state space enumeration algorithm (Appendix B.1). For instance, if the states in S can be addressed individually, Q can contain references to S instead of copies of states. In Spin [73, Chapter 13] and LoLA [136, Section 5.2], Q keeps track on the performed transitions, so that backtracking becomes a matter of "undoing" transitions.

Utilising Constraints. Maria encodes model states to bit strings before storing them [P2, Section 3.4]. In the bit strings, a data item that has been constrained to n possible values is represented with a fixed amount of  $\lceil \log_2 n \rceil$  bits. A variable-length representation is used for unconstrained multi-sets (Petri net places without capacity constraints). Places for which an invariant expression (a special case of the place invariants of algebraic system nets [98]) is given are omitted from the bit vector, since their markings can be recomputed.

Representing Sets with Graphs. If the reachable states follow some pattern, it can be efficient to represent them with a graph structure. The performance of Boolean Decision Diagrams [18] (BDD) greatly depends on the way how the system state is translated into Boolean variables and in which order these variables occur in the diagrams. Also, a BDD can consume more space when state space reductions are applied, since reductions remove regularity [156]. Graph Encoded Tuple Sets [62] (GETS) seem to yield good results even when partial order reduction is applied. However, this kind of dynamically growing and shrinking graph data structures tend to create very random access patterns with potentially large transformation steps. Thus, it is hard to implement them efficiently for other than uniprocessor systems working on central memory.

Hierarchal Representations. Comparable performance to GETS can be reached with the much simpler "collapse" option [62, Section 5.8] of Spin, which divides the state into process-specific components. The state is represented as a sequence of index numbers to component state sets. In modular state spaces, further savings may be achieved by representing

the nodes of the synchronisation graph with indexes to strongly connected components of the module state space graphs [29, Section 4.1].

Distributed Storage. There is a practical limit on the amount of main memory that can be easily installed in commonly available computing workstations. One way of gaining access to more storage space is utilising the networking capabilities of modern workstations. Schmidt [137] describes a tree data structure for representing the set of reachable states, and an algorithm that allows the migration of subtrees to other computing nodes. When a computing node is about to run out of memory, it can delegate work to other nodes. This should work better in dynamic environments than Parallel  $\text{Mur}\varphi$  [146], which distributes states among the workstations according to predefined hash signatures.

## Approximating the Set of Reachable States

The memory usage reduction methods discussed so far have one thing in common: when the state space exploration algorithm terminates without encountering any errors, the model is guaranteed to be error-free.

To save memory space, the set S of reachable states can be approximated with a one-way hash data structure. If the structure maps two states  $s \neq s'$  identically, the states reachable from s or s' may remain unexplored. In other words, the algorithm may produce *false positive* answers—claiming that the system is free of errors when it is not.

MARIA implements two methods of this kind: bit-state hashing [74, Section 3.4.2] and hash compaction [145, Section 2.3]. They can be used for estimating the lower bound of the state space graph size for models whose full state space graph would exceed the available memory capacity. These methods can reach nearly full coverage in a fraction of the storage capacity that would be needed for a full search.